T .s ,,IcoNv,,, I CALCO T,O.,.O,W,,.,N,X,,PO0.

FADD, L,~(~a~,EPO I START ITRANSFERI SYNCHRONIZE ~l

I

, ,,

EXCEPTION PROCESSING r I PROCESSING

EXCEPTION

HANDLER

FSAVE

8S;T 8IT 27 OF BIU FLAG

FRESTORE

RTE

INTERRUPT

HANDLER

FSAVE

FR;STORE

mE

I

--'--~"[ CONVERT I CALCULATE I STORE, [

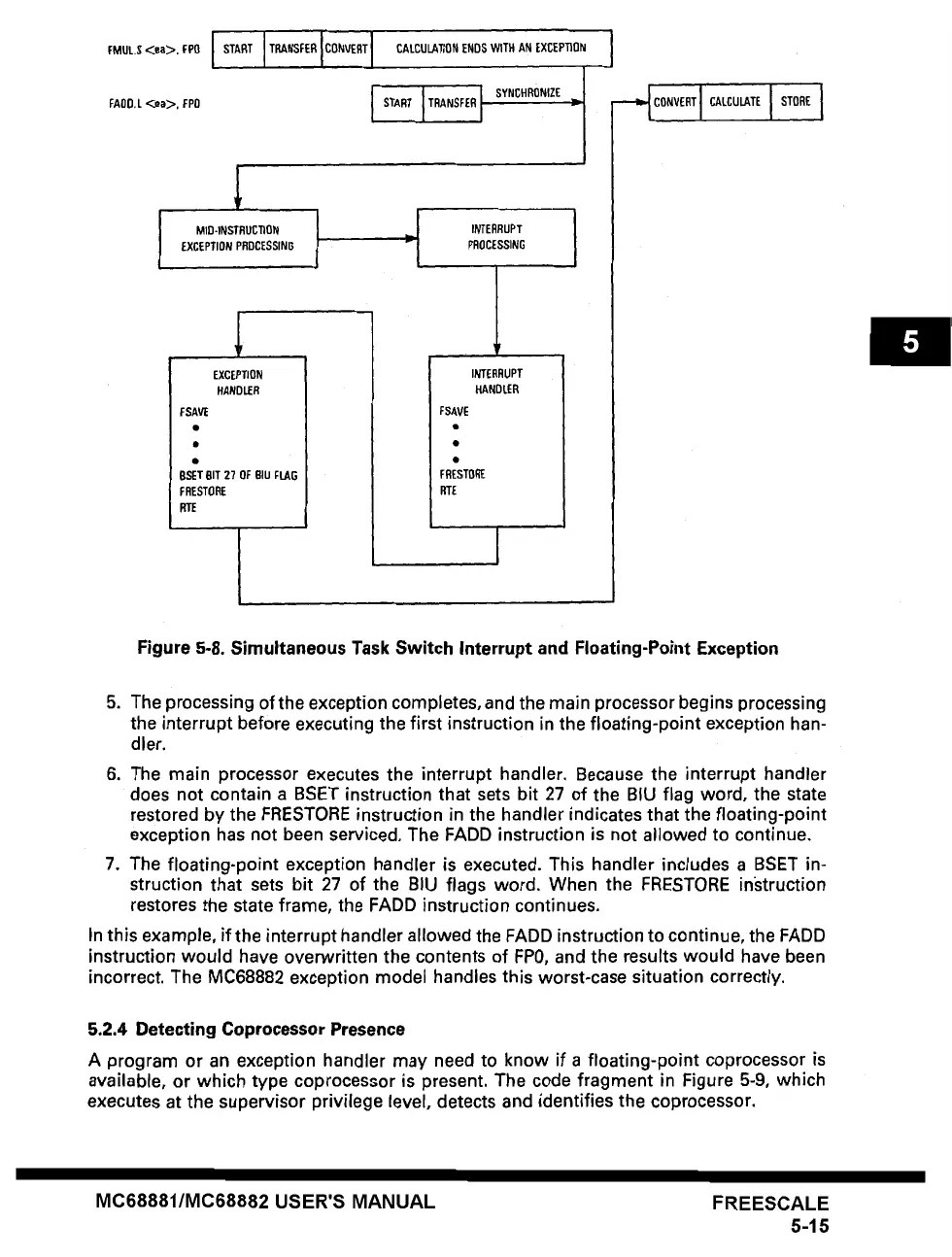

Figure 5-8. Simultaneous Task Switch Interrupt and Floating-Point Exception

5. The processing of the exception completes, and the main processor begins processing

the interrupt before executing the first instruction in the floating-point exception han-

dler.

6. The main processor executes the interrupt handler. Because the interrupt handler

does not contain a BSET instruction that sets bit 27 of the BIU flag word, the state

restored by the FRESTORE instruction in the handler indicates that the floating-point

exception has not been serviced. The FADD instruction is not allowed to continue.

7. The floating-point exception handler is executed. This handler includes a BSET in-

struction that sets bit 27 of the BIU flags word. When the FRESTORE instruction

restores the state frame, the FADD instruction continues.

In this example, if the interrupt handler allowed the FADD instruction to continue, the FADD

instruction would have overwritten the contents of FP0, and the results would have been

incorrect. The MC68882 exception model handles this worst-case situation correctly.

5.2.4 Detecting Coprocessor Presence

A program or an exception handler may need to know if a floating-point

coprocessor

is

available, or which type coprocessor is present. The code fragment in Figure 5-9, which

executes at the supervisor privilege level, detects and identifies the coprocessor.

MC68881/MC68882 USER'S MANUAL

FREESCALE

5-15

Loading...

Loading...