6

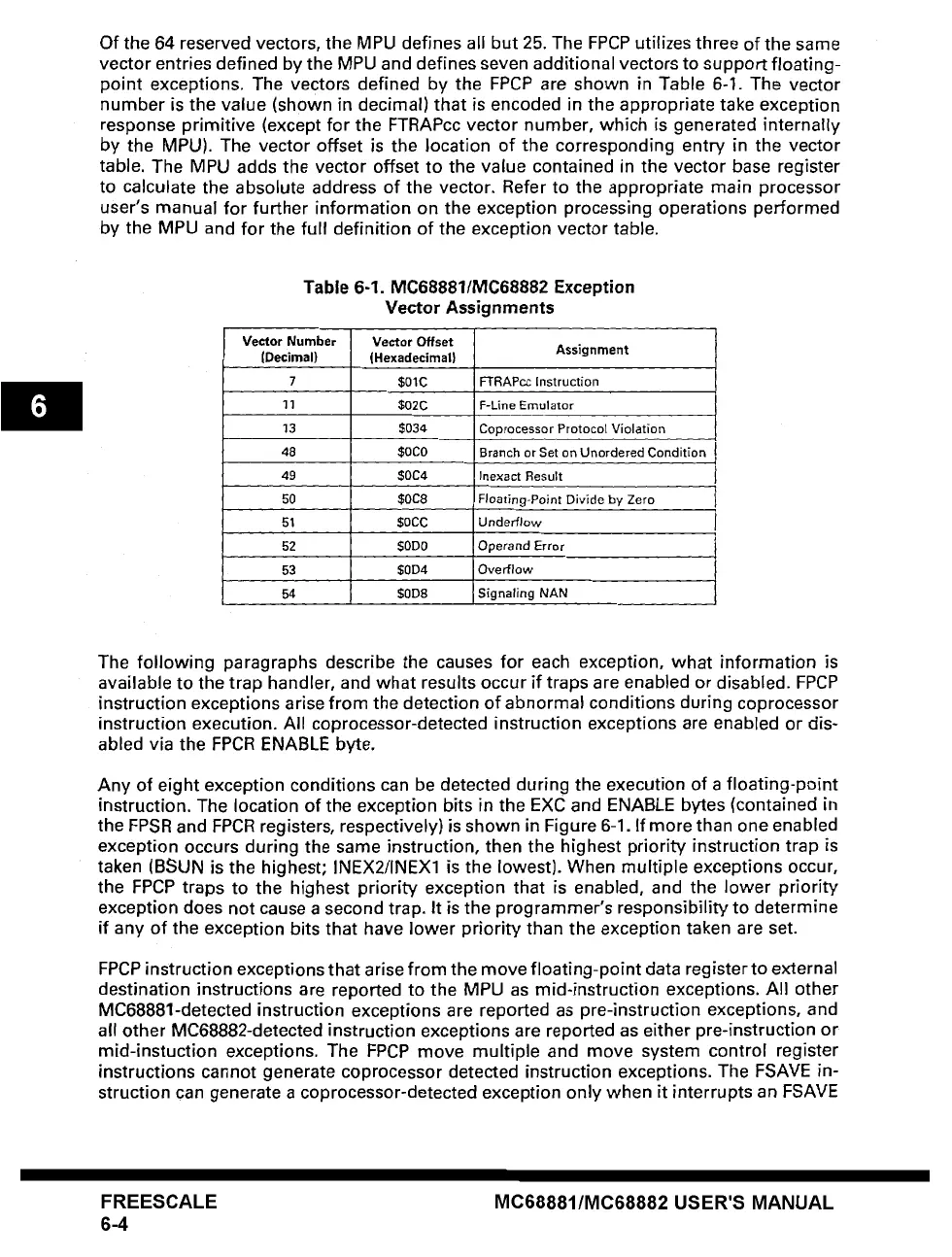

Of the 64 reserved vectors, the MPU defines all but 25. The FPCP utilizes three of the same

vector entries defined by the MPU and defines seven additional vectors to support floating-

point exceptions. The vectors defined by the FPCP are shown in Table 6-1. The vector

number is the value (shown in decimal) that is encoded in the appropriate take exception

response primitive (except for the FTRAPcc vector number, which is generated internally

by the MPU). The vector offset is the location of the corresponding entry in the vector

table. The MPU adds the vector offset to the value contained in the vector base register

to calculate the absolute address of the vector. Refer to the appropriate main processor

user's manual for further information on the exception processing operations performed

by the MPU and for the full definition of the exception vector table.

Table 6-1. MC68881/MC68882 Exception

Vector Assignments

Vector Number Vector Offset

(Decimal) (Hexadecimal) Assignment

7 $01C FTRAPcc Instruction

11 $02C F-Line Emulator

13 $034 Coprocessor Protocot Violation

48 $0C0 Branch or Set on Unordered Condition

49 $0C4 Inexact Result

50 $0C8 Floating-Point Divide by Zero

51 $0CC Underflow

52 $0D0 Operand Error

53 $0D4 Overflow

54 $0D8 Signaling NAN

The following paragraphs describe the causes for each exception, what information is

available to the trap handler, and what results occur if traps are enabled or disabled. FPCP

instruction exceptions arise from the detection of abnormal conditions during coprocessor

instruction execution. All coprocessor-detected instruction exceptions are enabled or dis-

abled via the FPCR ENABLE byte.

Any of eight exception conditions can be detected during the execution of a floating-point

instruction. The location of the exception bits in the EXC and ENABLE bytes (contained in

the FPSR and FPCR registers, respectively) is shown in Figure 6-1. If more than one enabled

exception occurs during the same instruction, then the highest priority instruction trap is

taken (BSUN is the highest; INEX2/INEX1 is the lowest). When multiple exceptions occur,

the FPCP traps to the highest priority exception that is enabled, and the lower priority

exception does not cause a second trap. It is the programmer's responsibility to determine

if any of the exception bits that have lower priority than the exception taken are set.

FPCP instruction exceptions that arise from the move floating-point data register to external

destination instructions are reported to the MPU as mid-instruction exceptions. All other

MC68881-detected instruction exceptions are reported as pre-instruction exceptions, and

all other MC68882-detected instruction exceptions are reported as either pre-instruction or

mid-instuction exceptions. The FPCP move multiple and move system control register

instructions cannot generate coprocessor detected instruction exceptions. The FSAVE in-

struction can generate a coprocessor-detected exception only when it interrupts an FSAVE

FREESCALE

6-4

MC68881/MC68882 USER'S MANUAL

Loading...

Loading...