30

0

0

0

0

1

1

1

1

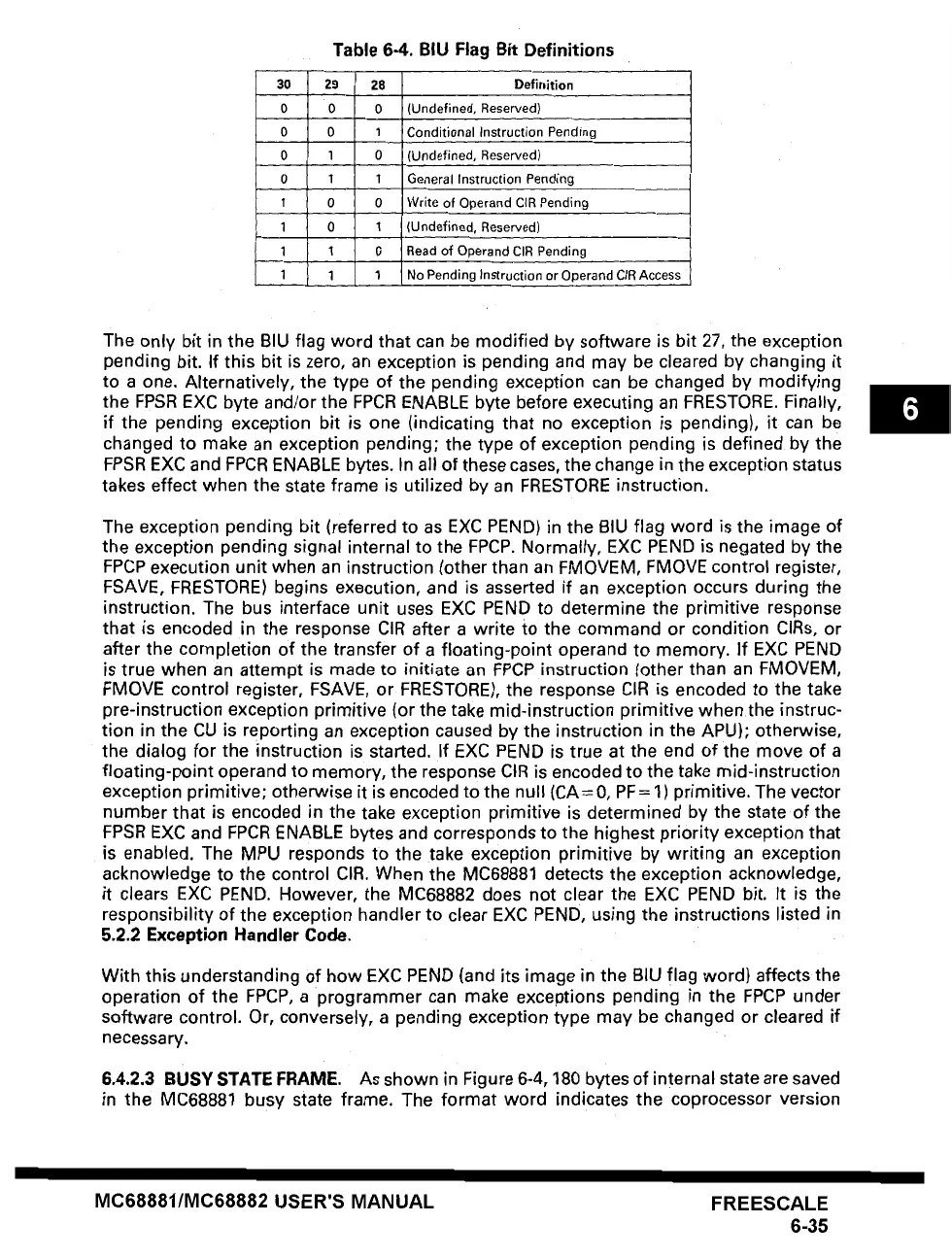

Table 6-4. BIU Flag Bit Definitions

29 28 Definition

0 0 , (Undefined, Reserved)

0 1 ' Conditional instruction Pending

1 0 ! (Undefined, Reserved)

1 1 General Instruction Pending

0 0 Write of Operand CiR Pendin 9

0 1 (Undefined, Reserved)

1 0 Read of Operand CIR Pending

1 1 No Pending Instruction or Operand CIR Access

The only bit in the BIU flag word that can be modified by software is bit 27, the exception

pending bit. If this bit is zero, an exception is pending and may be cleared by changing it

to a one. Alternatively, the type of the pending exception can be changed by modifying

the FPSR EXC byte and/or the FPCR ENABLE byte before executing an FRESTORE. Finally,

if the pending exception bit is one (indicating that no exception is pending), it can be

changed to make an exception pending; the type of exception pending is defined by the

FPSR EXC and FPCR ENABLE bytes. In all of these cases, the change in the exception status

takes effect when the state frame is utilized by an FRESTORE instruction.

The exception pending bit (referred to as EXC PEND) in the BIU flag word is the image of

the exception pending signal internal to the FPCP. Normally, EXC PEND is negated by the

FPCP execution unit when an instruction (other than an FMOVEM, FMOVE control register,

FSAVE, FRESTORE) begins execution, and is asserted if an exception occurs during the

instruction. The bus interface unit uses EXC PEND to determine the primitive response

that is encoded in the response CIR after a write to the command or condition CIRs, or

after the completion of the transfer of a floating-point operand to memory. If EXC PEND

is true when an attempt is made to initiate an FPCP instruction (other than an FMOVEM,

FMOVE control register, FSAVE, or FRESTORE), the response CIR is encoded to the take

pre-instruction exception primitive (or the take mid-instruction primitive when the instruc-

tion in the CU is reporting an exception caused by the instruction in the APU); otherwise,

the dialog for the instruction is started. If EXC PEND is true at the end of the move of a

floating-point operand to memory, the response CIR is encoded to the take mid-instruction

exception primitive; otherwise it is encoded to the null (CA= 0, PF = 1) primitive. The vector

number that is encoded in the take exception primitive is determined by the state of the

FPSR EXC and FPCR ENABLE bytes and corresponds to the highest priority exception that

is enabled. The MPU responds to the take exception primitive by writing an exception

acknowledge to the control CIR. When the MC68881 detects the exception acknowledge,

it clears EXC PEND. However, the MC68882 does not clear the EXC PEND bit. It is the

responsibility of the exception handler to clear EXC PEND, using the instructions listed in

5.2.2 Exception Handler Code,

With this understanding of how EXC PEND (and its image in the BIU flag word) affects the

operation of the FPCP, a programmer can make exceptions pending in the FPCP under

software control. Or, conversely, a pending exception type may be changed or cleared if

necessary.

6.4.2.3 BUSY STATE FRAME. As shown in Figure 6-4, 180 bytes of internal state are saved

in the MC68881 busy state frame. The format word indicates the coprocessor version

MC68881/MC68882 USER'S MANUAL FREESCALE

6-35

Loading...

Loading...