with the corresponding times using the MC68882. The first column lists the instructions

in the set. The second column lists the time required to obtain the operand at the effective

address. These numbers are taken from Table 8-1. This time applies to both coprocessors;

it is added to the execution time for the instruction. The third column lists the total execution

times for each instruction when executing in the MC68881.

The four columns to the right list values that apply to the MC68882. From left to right, the

columns contain the following values:

1. The overall execution time for each instruction when executing in the MC68882, and

the H and T numbers for each of the instructions. The T values for the fully-concurrent

FMOVE instructions are shown as T = *

2. The adjusted head time, which is the sum of the effective address calculation time

and the head time. For the FMOVE to memory instructions (opclass 011 ), the effective

address calculation is not added to the head time. The tail time is not altered.

3. The effective head and effective tail time for each instruction. Where T is shown as

T= *, the effective head time is the sum of the FMOVE H time plus the H time of the

subsequent instruction. The tail time is not altered.

4. The actual overlap time, which is the lesser of the effective tail and the effective head

of the column to the left.

At the bottom of the table, the totals show the overall times. For the MC68881, this time

is the sum of the total execution time plus the effective address time. For the MC68882, it

is the sum of the total execution time plus the effective address time, less the actual overlap

time. The conclusion is that for the instruction sequence shown here, the MC68881 required

1.80 times longer to execute compared to the MC68882.

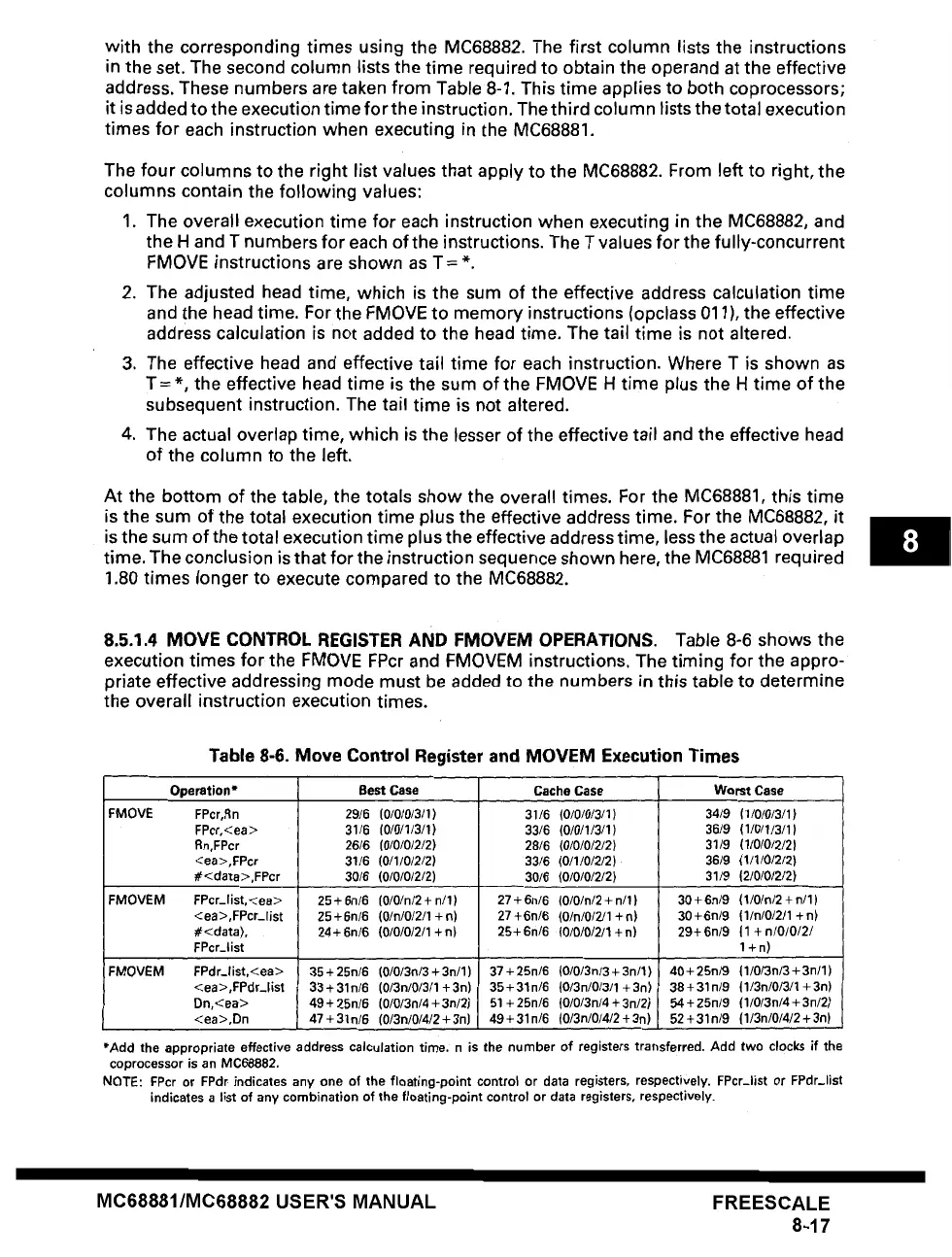

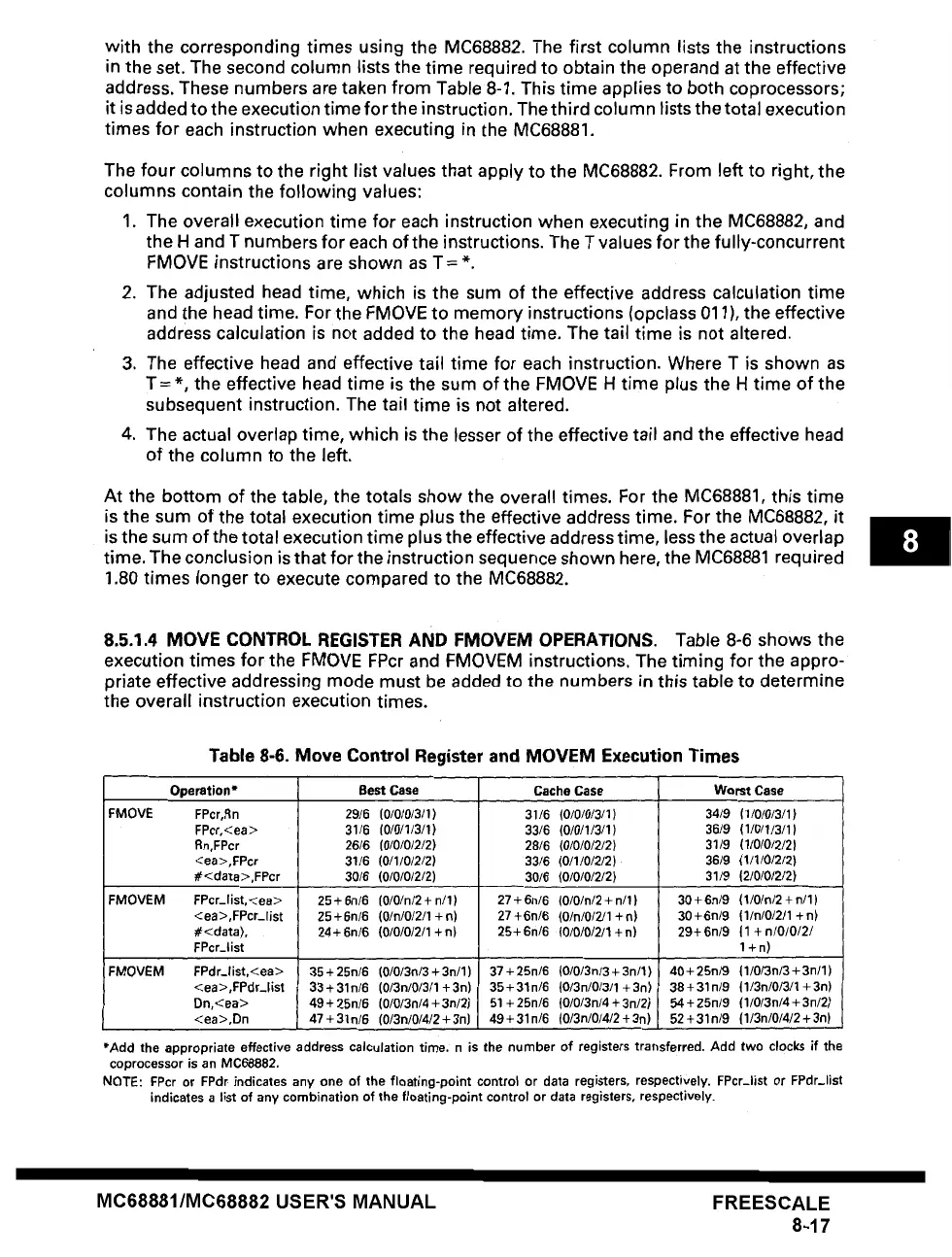

8.5.1.4 MOVE CONTROL REGISTER AND FMOVEM OPERATIONS.

Table 8-6 shows the

execution times for the FMOVE FPcr and FMOVEM instructions. The timing for the appro-

priate effective addressing mode must be added to the numbers in this table to determine

the overall instruction execution times.

Table 8-6, Move Control Register and MOVEM Execution Times

Operation* Rest Case Cache Case Worst Case

FMOVE FPcr,Rn 29/6 (0/0/0/3/1) 31/6 (0/0/0/3/1) 34/9 (1/0/0/3/1)

FPcr,<ea> 31/6 (0/0/1/3/1) 33/6 (0/0/1/3/1) 36/9 (1/0/1/3/1)

Rn,FPcr 26/6 (0/0/0/2/2) 28/6 (0/0/0/2/2) 31/9 (1/0/0/2/2)

<ea>,FPcr 31/6 (0/110/2/2) 3316

(0llf0/2/2)

36/9 {1tl/0/2/2)

#<data>,FPcr 30/6 (0/0/0/2/2) 30/6 (0/0/0/2/2) 31/9 (2/0/0/2/2)

FMOVEM FPcr_list,<ea> 25+6n/6 {0/0/n/2+n/1) 27+6n/6 (0/0/n/2+n/1) 30+6n/9 (1/0/n/2+n/1)

<ea>,FPcr_list 25+6n/6 (0/n/0/2/l+n) 27+6n/6 (0/n/0/2/l+n) 30+6n/9 (1/n/0/2/1 +n)

#<data), 24+6n/6 {0/0/0/2/1+n) 25+6n/6

(0t010/2/1+n)

29+6n/9 (1+n/0/0/2/

FPcr_iist 1 +n)

FMOVEM FPdr_list,<ea> 35 + 25n/6 (0/0/3n/3 ÷ 3n/1 ) 37 + 25n/6 (0/0/3n/3 + 3n/1) 40 + 25n/9 (1/0/3n/3 + 3n/1 )

<ea>,FPdr_list 33+31n/6 (0/3n/0/3/l+3n) 35+31n/6 (0/3n/0/3/1 +3n) 38+31n/9

(1/3n/0/3/1

+3n)

Dn,<ea> 49+25n/6 (0/0/3n/4+3n/2) 61+25n/6 (0/0/3n/4+3n/2) 54+25n/9 (1/0/3n/4+3n/2)

<ea>,Dn 47+31n/6

(O/3n/O/4/2+3n}

49+31n/6 (0/3n/0/4/2+3n) 52+31n/9

(1/3n/O/4/2+3n)

*Add the appropriate effective address calculation time. n is the number of registers transferred. Add two clocks if the

coprocessor is an MC68882.

NOTE:

FPcr or FPdr indicates any one of the floating-polnt control or data registers, respectively. FPcr-list or FPdr_list

indicates a list of any combination of the floating-point control or data registers, respectively.

MC68881/MC68882 USER'S MANUAL

FREESCALE

8-17

Loading...

Loading...