7

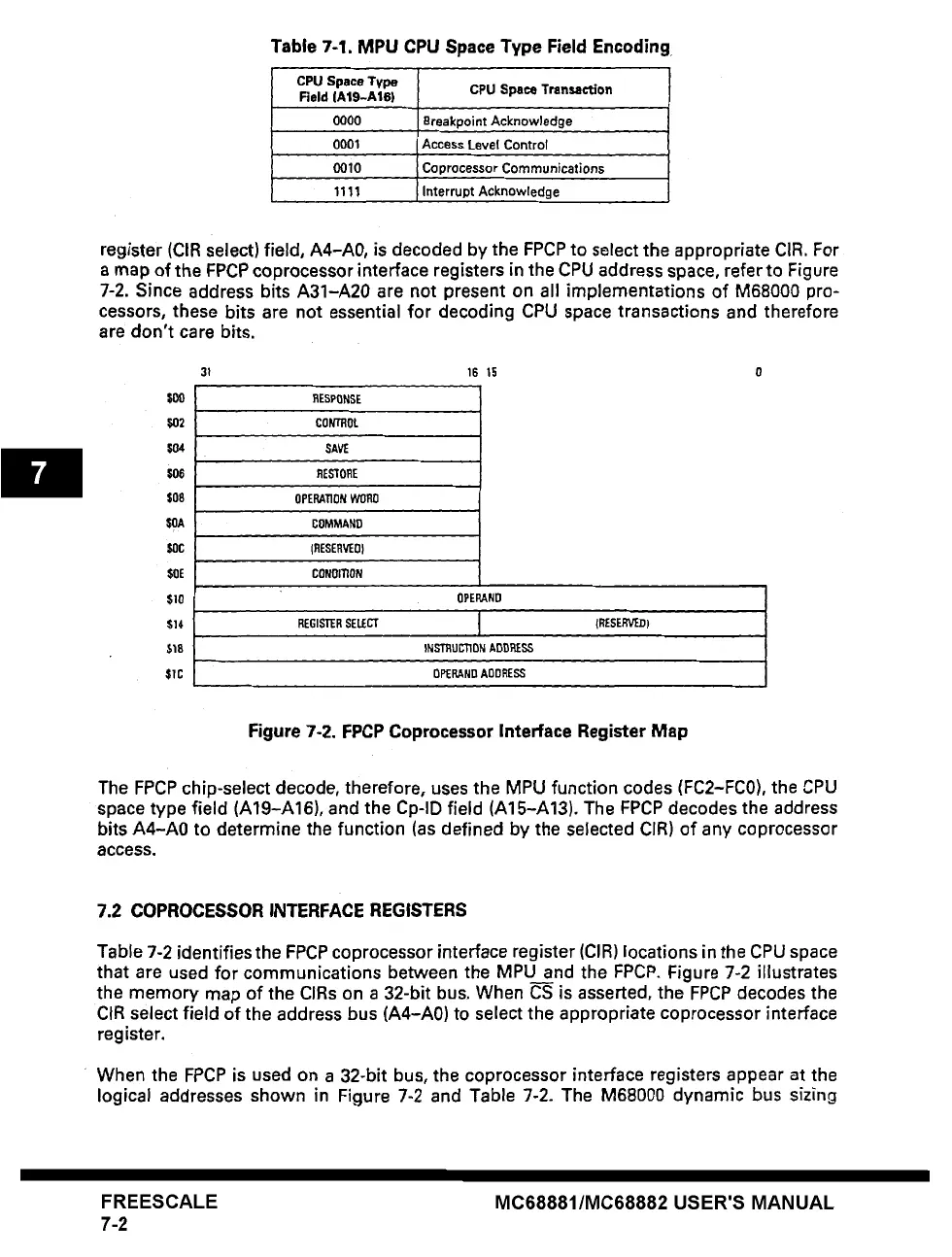

Table 7-1. MPU CPU Space Type Field Encoding

CPU Space

Type CPU Space Transaction

Field (A19-A16)

0000 Breakpoint Acknowledge

0001 Access Level Control

0010 Coprocessor Communications

1111 Interrupt Acknowledge

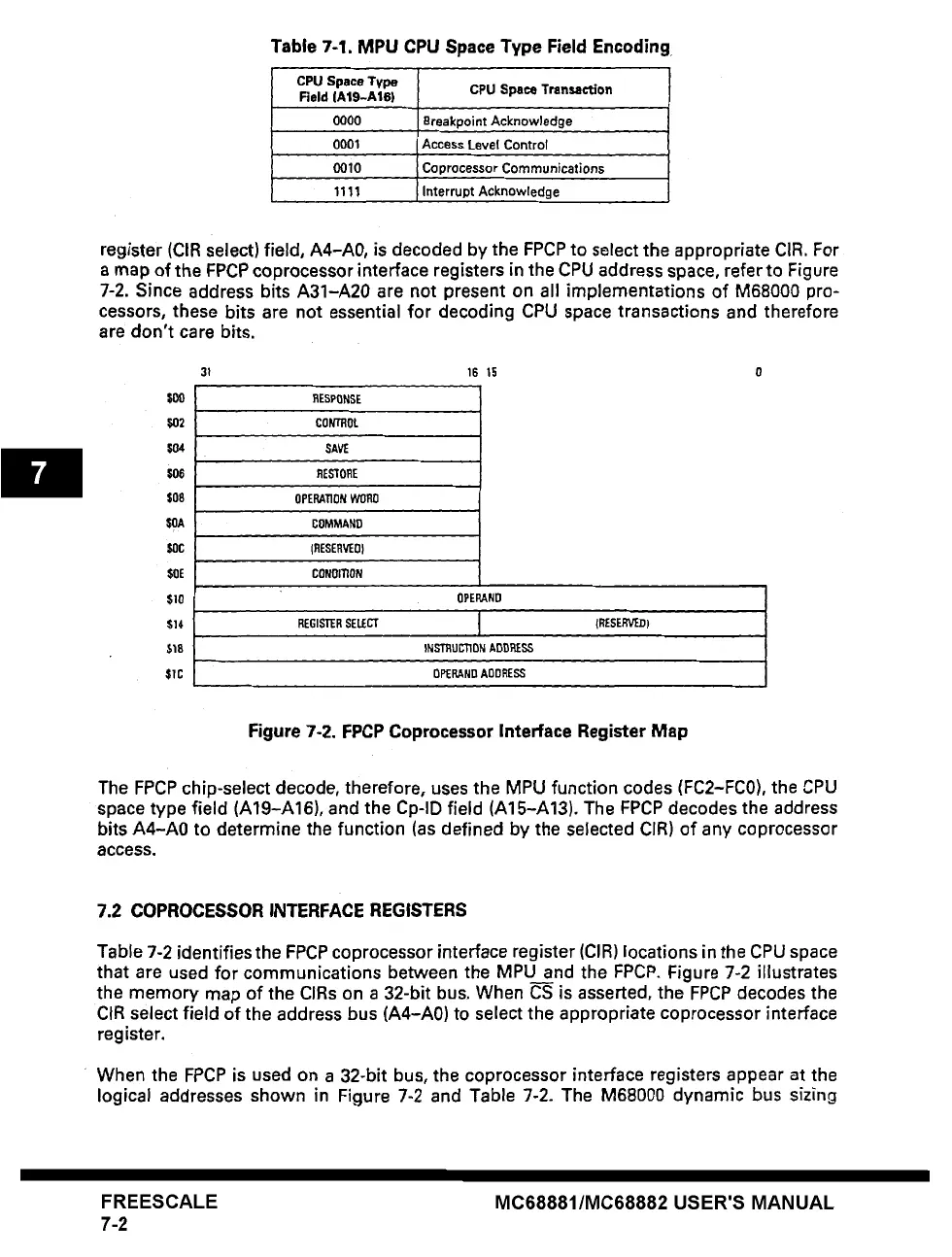

register (CIR select) field, A4-A0, is decoded by the FPCP to select the appropriate CIR. For

a map of the FPCP coprocessor interface registers in the CPU address space, refer to Figure

7-2. Since address bits A31-A20 are not present on all implementations of M68000 pro-

cessors, these bits are not essential for decoding CPU space transactions and therefore

are don't care bits.

SOS

$O2

$O4

sos

SOS

$OA

=OC

$OE

$10

$14

$18

$1C

31

RESPONSE

CONTROL

SAVE

RESTORE

OPERATION WORO

COMMAND

(RESEflVEO)

CONDITION

16 15 0

0tOERAND

REGISTER SELECT I (RESERVED)

i

INSTRUL'~rlON ADDP~SS

OPERAND ADDRESS

Figure 7-2. FPCP Coprocessor Interface Register Map

The FPCP chip-select decode, therefore, uses the MPU function codes (FC2-FC0), the CPU

space type field (A19-A16), and the Cp-ID field (A15-A13). The FPCP decodes the address

bits A4-A0 to determine the function (as defined by the selected CIR) of any coprocessor

access.

7.2 COPROCESSOR INTERFACE REGISTERS

Table 7-2 identifies the FPCP coprocessor interface register (CIR) locations in the CPU space

that are used for communications between the MPU and the FPCP. Figure 7-2 illustrates

the memory map of the CIRs on a 32-bit bus. When CS is asserted, the FPCP decodes the

CIR select field of the address bus (A4-A0) to select the appropriate coprocessor interface

register.

When the FPCP is used on a 32-bit bus, the coprocessor interface registers appear at the

logical addresses shown in Figure 7-2 and Table 7-2. The M68000 dynamic bus sizing

FREESCALE

7-2

MC68881/MC68882 USER'S MANUAL

Loading...

Loading...