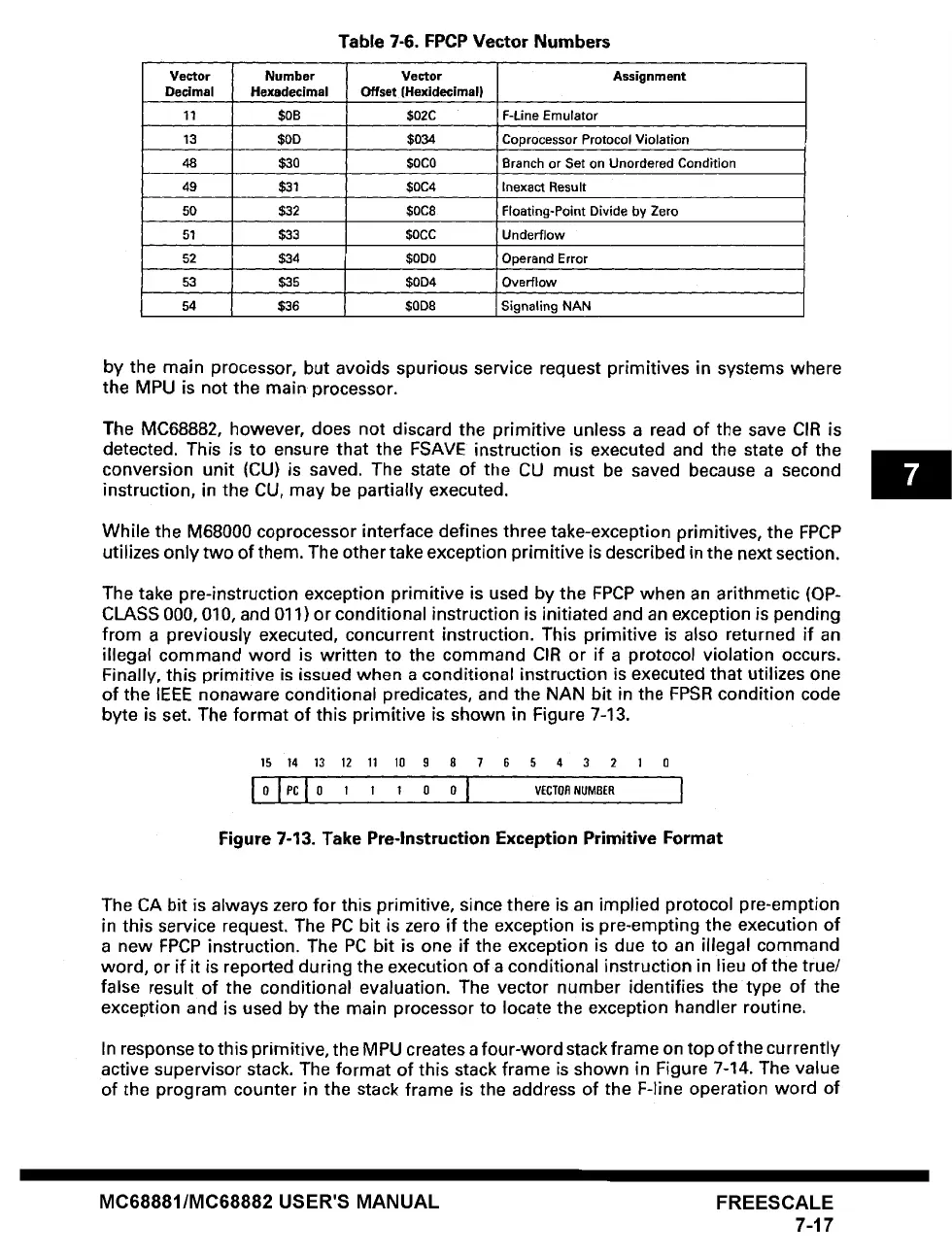

Table 7-6. FPCP Vector Numbers

Vector Number Vector Assignment

Decimal Hexadecimal Offset (Hexidecimal)

11 $0B $02C F-Line Emulator

13 $0D $034 Coprocessor

Protocol

Violation

48 $30 $0CO Branch or Set on Unordered Condition

49 $31 $0C4 Inexact Result

50 $32 $0C8 Floating-Point Divide by Zero

51 $33 $0CC Underflow

52 $34 $0D0 Operand

Error

53 $35 $0D4 Overflow

54 $36 $0D8 Signaling NAN

by the main processor, but avoids spurious service request primitives in systems where

the MPU is not the main processor.

The MC68882, however, does not discard the primitive unless a read of the save CIR is

detected. This is to ensure that the FSAVE instruction is executed and the state of the

conversion unit (CU) is saved. The state of the CU must be saved because a second

instruction, in the CU, may be partially executed.

While the M68000 coprocessor interface defines three take-exception primitives, the FPCP

utilizes only two of them. The other take exception primitive is described in the next section.

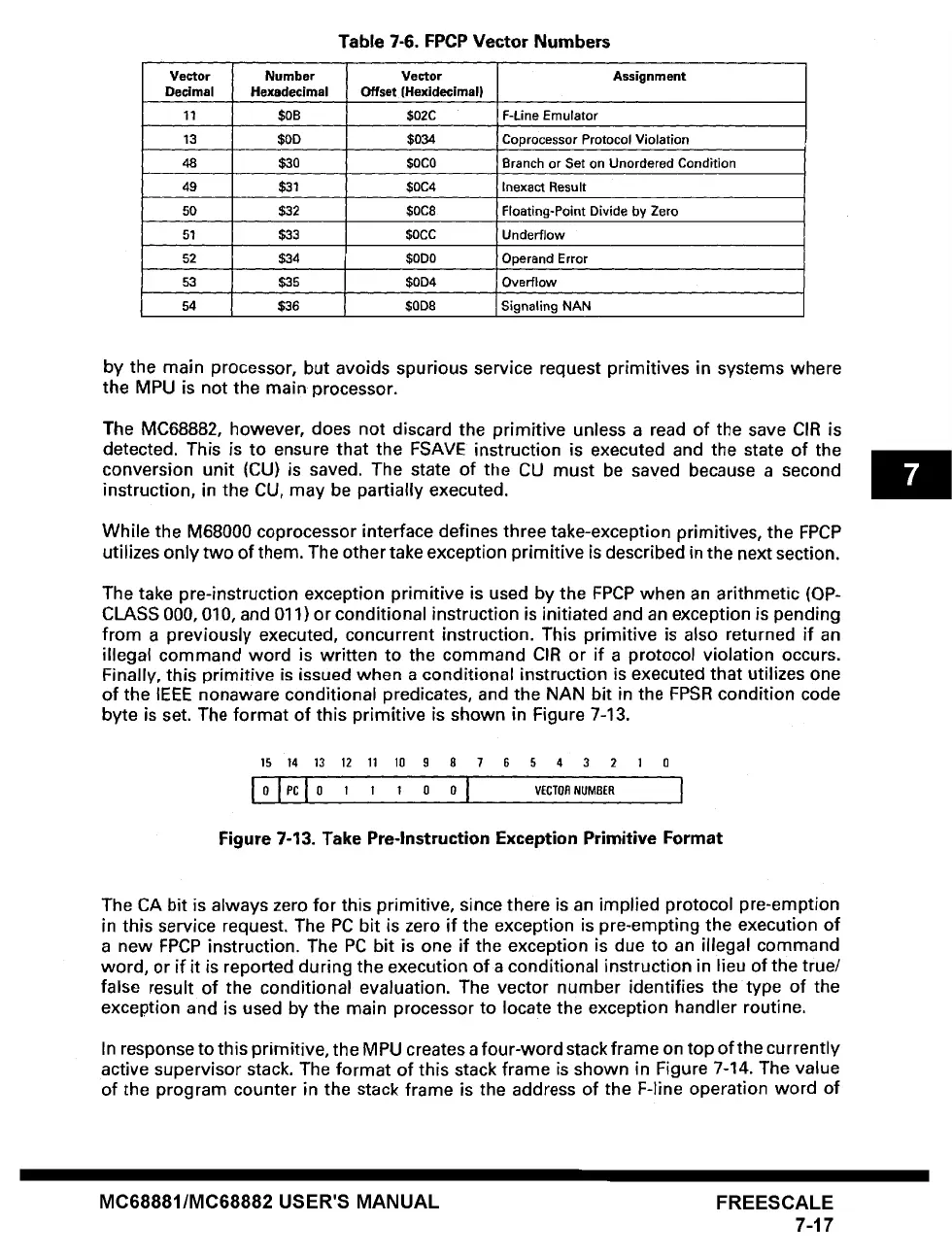

The take pre-instruction exception primitive is used by the FPCP when an arithmetic (OP-

CLASS 000, 010, and 011) or conditional instruction is initiated and an exception is pending

from a previously executed, concurrent instruction. This primitive is also returned if an

illegal command word is written to the command CIR or if a protocol violation occurs.

Finally, this primitive is issued when a conditional instruction is executed that utilizes one

of the IEEE nonaware conditional predicates, and the NAN bit in the FPSR condition code

byte is set. The format of this primitive is shown in Figure 7-13.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 l 0

Figure 7-13. Take Pre-lnstruction Exception Primitive Format

The CA bit is always zero for this primitive, since there is an implied protocol pre-emption

in this service request. The PC bit is zero if the exception is pre-empting the execution of

a new FPCP instruction. The PC bit is one if the exception is due to an illegal command

word, or if it is reported during the execution of a conditional instruction in lieu of the true/

false result of the conditional evaluation. The vector number identifies the type of the

exception and is used by the main processor to locate the exception handler routine.

In response to this primitive, the MPU creates a four-word stack frame on top of the currently

active supervisor stack. The format of this stack frame is shown in Figure 7-14. The value

of the program counter in the stack frame is the address of the F-line operation word of

MC68881/MC68882 USER'S MANUAL

FREESCALE

7-17

Loading...

Loading...