2

or double precision mode is selected, the exponent value is in the correct range for the

single or double precision format (although it is stored in extended precision format). An

important exception to this rule is for the FSGLDIV and FSGLMUL instructions. Regardless

of the precision specified by the PREC bits, these instructions round the result mantissa

to single precision and generate an extended precision exponent which may be out of

range for a single precision number.

If the destination is a memory location, the PREC bits are ignored. In this case, a number

in the extended precision format is taken from the source floating-point data register,

rounded to the destination format precision, and written to memory.

The execution speed of all instructions is degraded significantly when single and double

precision rounding modes are used. Because these modes are intended to be used for

emulation, this reduction is not detrimental. When operating in these modes, the FPCP

produces the same result as any other machine that conforms to the IEEE standard without

supporting extended precision calculations. However, the result obtained by performing a

series of operations with single or double precision rounding may not be the same as the

result of performing the same operations in extended precision and storing the final result

in the single or double precision format.

2.3 FLOATING-POINT STATUS REGISTER

The floating-point status register (FPSR) contains a floating-point condition code byte, a

floating-point exception status byte, quotient bits, and a floating-point accrued exception

byte. All bits in the FPSR can be read or written by the user. Execution of most floating-

point instructions modifies this register.

The reset function or a restore operation of the null state clears the FPSR.

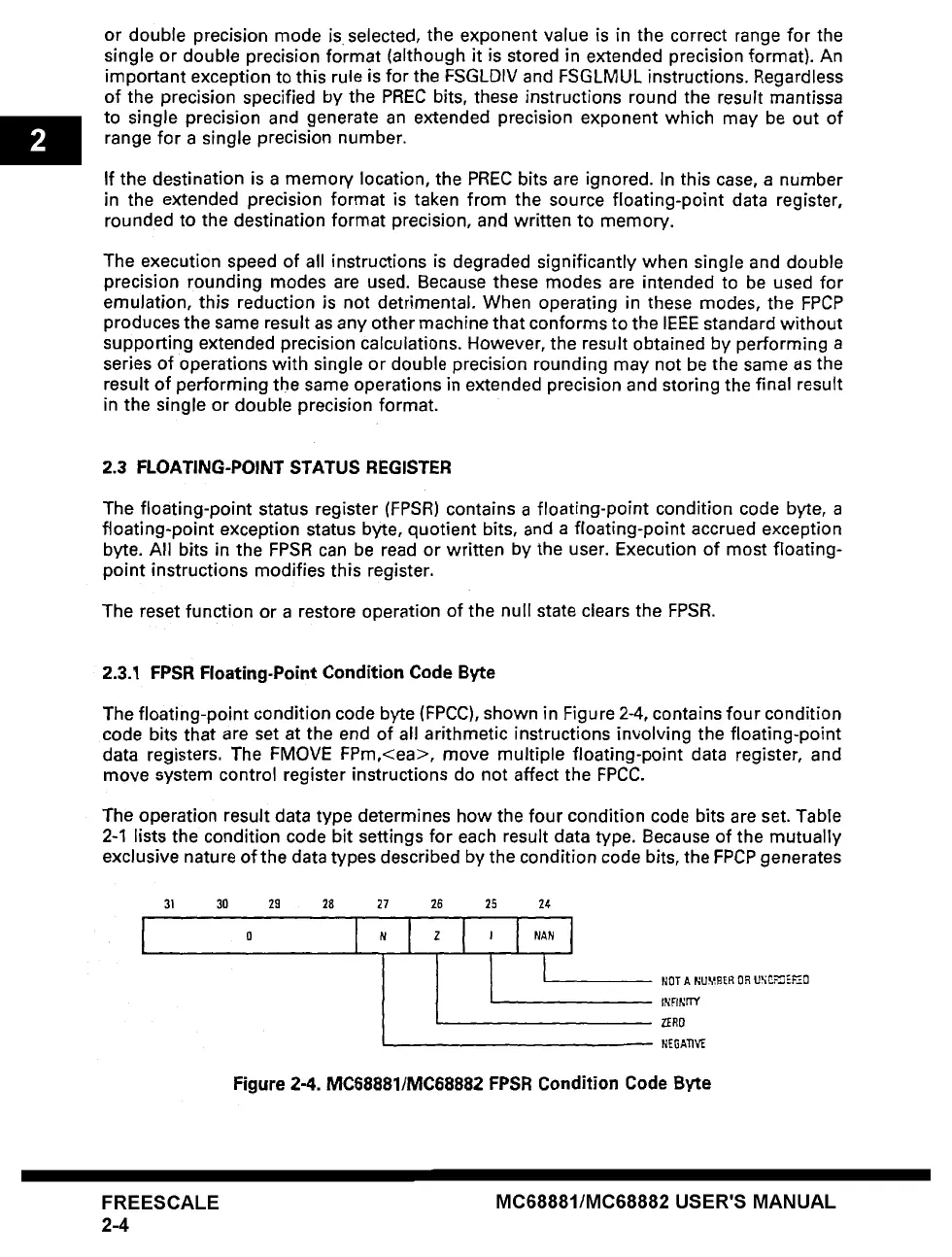

2.3.1 FPSR Floating-Point Condition Code Byte

The floating-point condition code byte (FPCC), shown in Figure 2-4, contains four condition

code bits that are set at the end of all arithmetic instructions involving the floating-point

data registers. The FMOVE FPm,<ea>, move multiple floating-point data register, and

move system control register instructions do not affect the FPCC.

The operation result

data

type determines how the four condition code bits are set. Table

2-1 lists the condition code bit settings for each result data type. Because of the mutually

exclusive nature of the data types described by the condition code bits, the FPCP generates

31 30 29 28 27 26 25 24

NOTA NUMEER 0.R UNOF~E~O

INRNFrY

Z1ER0

NEGA~VE

Figure 2-4. MC68881/MC68882 FPSR Condition Code Byte

FREESCALE

2-4

MC68881/MC68882 USER'S MANUAL

Loading...

Loading...