6

6.1.6 Divide-by-Zero

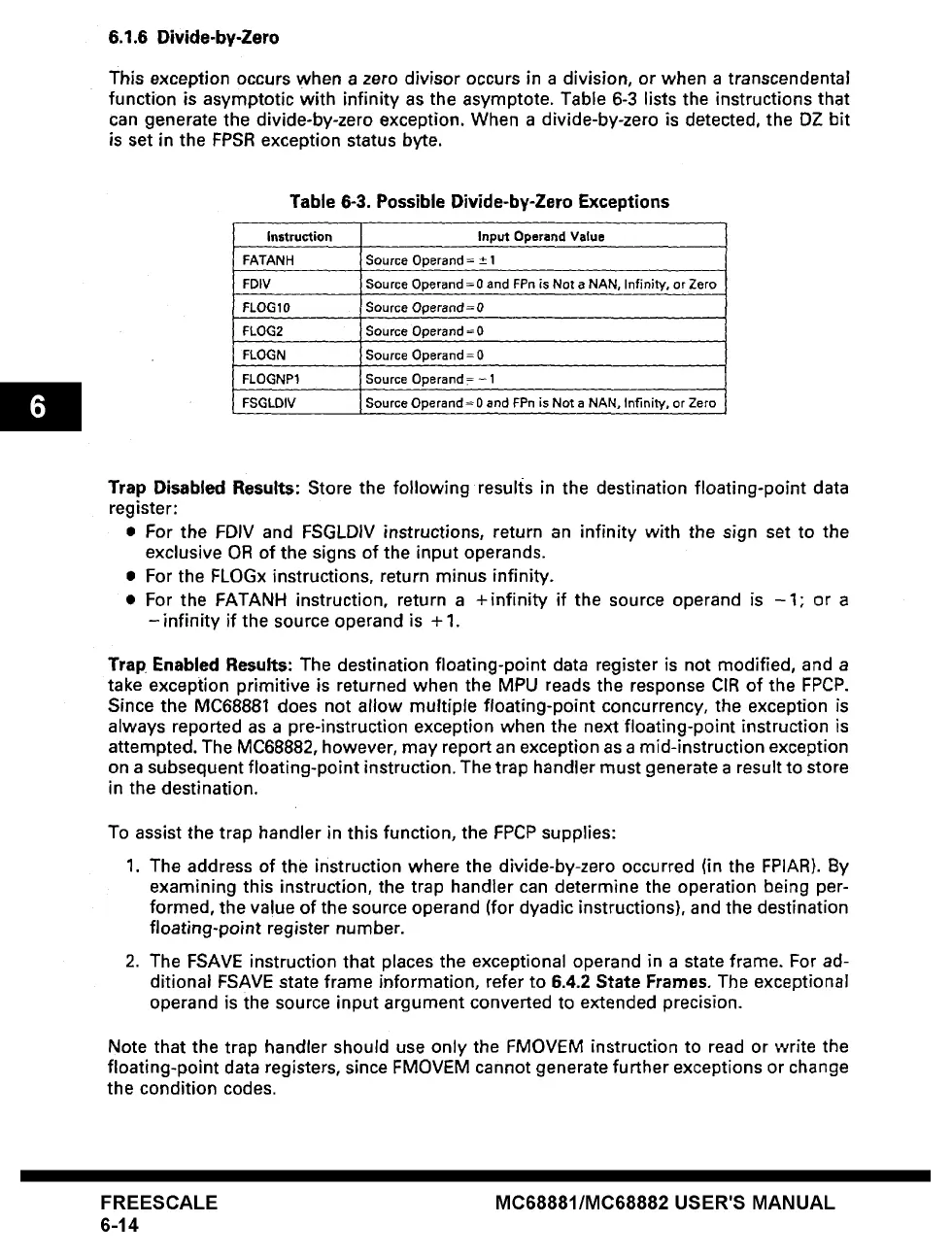

This exception occurs when a zero divisor occurs in a division, or when a transcendental

function is asymptotic with infinity as the asymptote. Table 6-3 lists the instructions that

can generate the divide-by-zero exception. When a divide-by-zero is detected, the DZ bit

is set in the FPSR exception status byte.

Table 6-3. Possible Divide-by-Zero Exceptions

Instruction Input

Operand Value

FATANH Source Operand = +- 1

FDIV Source Operand =0 and FPn is Not a NAN, Infinity, or Zero

FLOG 10 Source

Operand=O

FLOG2 Source Operand = 0

FLOGN Source Operand = 0

FLOGNP1 Source Operand- - 1

FSGLDIV Source Operand=0 and FPn is Not a NAN, Infinity, or Zero

Trap Disabled Results:

Store the following results in the destination floating-point data

register:

• For the FDIV and FSGLDIV instructions, return an infinity with the sign set to the

exclusive OR of the signs of the input operands.

• For the FLOGx instructions, return minus infinity.

• For the FATANH instruction, return a +infinity if the source operand is -1; or a

-infinity if the source operand is + 1.

Trap Enabled Results:

The destination floating-point data register is not modified, and a

take exception primitive is returned when the MPU reads the response CIR of the FPCP.

Since the MC68881 does not allow multiple floating-point concurrency, the exception is

always reported as a pre-instruction exception when the next floating-point instruction is

attempted. The MC68882, however, may report an exception as a mid-instruction exception

on a subsequent floating-point instruction. The trap handler must generate a result to store

in the destination.

To assist the trap handler in this function, the FPCP supplies:

1. The address of the instruction where the divide-by-zero occurred (in the FPIAR}. By

examining this instruction, the trap handler can determine the operation being per-

formed, the value of the source operand (for dyadic instructions), and the destination

floating-point

register number.

2. The FSAVE instruction that places the exceptional operand in a state frame. For ad-

ditional FSAVE state frame information, refer to 6.4.2

State Frames.

The exceptional

operand is the source input argument converted to extended precision.

Note that the trap handler should use only the FMOVEM instruction to read or write the

floating-point data registers, since FMOVEM cannot generate further exceptions or change

the condition codes.

FREESCALE

6-14

MC68881/MC68882 USER'S MANUAL

Loading...

Loading...