5

indicates that the main processor should perform the specified service and then read the

response CIR again. The FPCP sets the CA bit to define portions of the floating-point

instruction that cannot operate concurrently with main processor instruction execution.

When the coprocessor can operate concurrently with main processor instructions, it clears

the CA bit in the response primitive. Clearing the CA allows the main processor to proceed

to the next instruction after it has read the response CIR and performed the specified

service. This releases the main processor for concurrent operation. In the arithmetic

floating-point instructions, the FPCP releases the main processor after the transfer phase

is completed. Refer to 8.2 CONCURRENT INSTRUCTION EXECUTION for further details of

main processor/coprocessor concurrent instruction execution.

Within the boundaries of a floating-point instruction

that does not al]ow concurrency with

main processor instructions (response primitives return CA= 1), the FPCP can allow the

main processor to service pending interrupts. Bit [8] of the null primitive is the interrupts

allowed (IA) bit, used by the FPCP to allow the main processor to check for pending

interrupts and to service them before reading the response CIR again. This minimizes the

worst case interrupt latency. Refer to 8.3 INTERRUPT LATENCY TIMES for details.

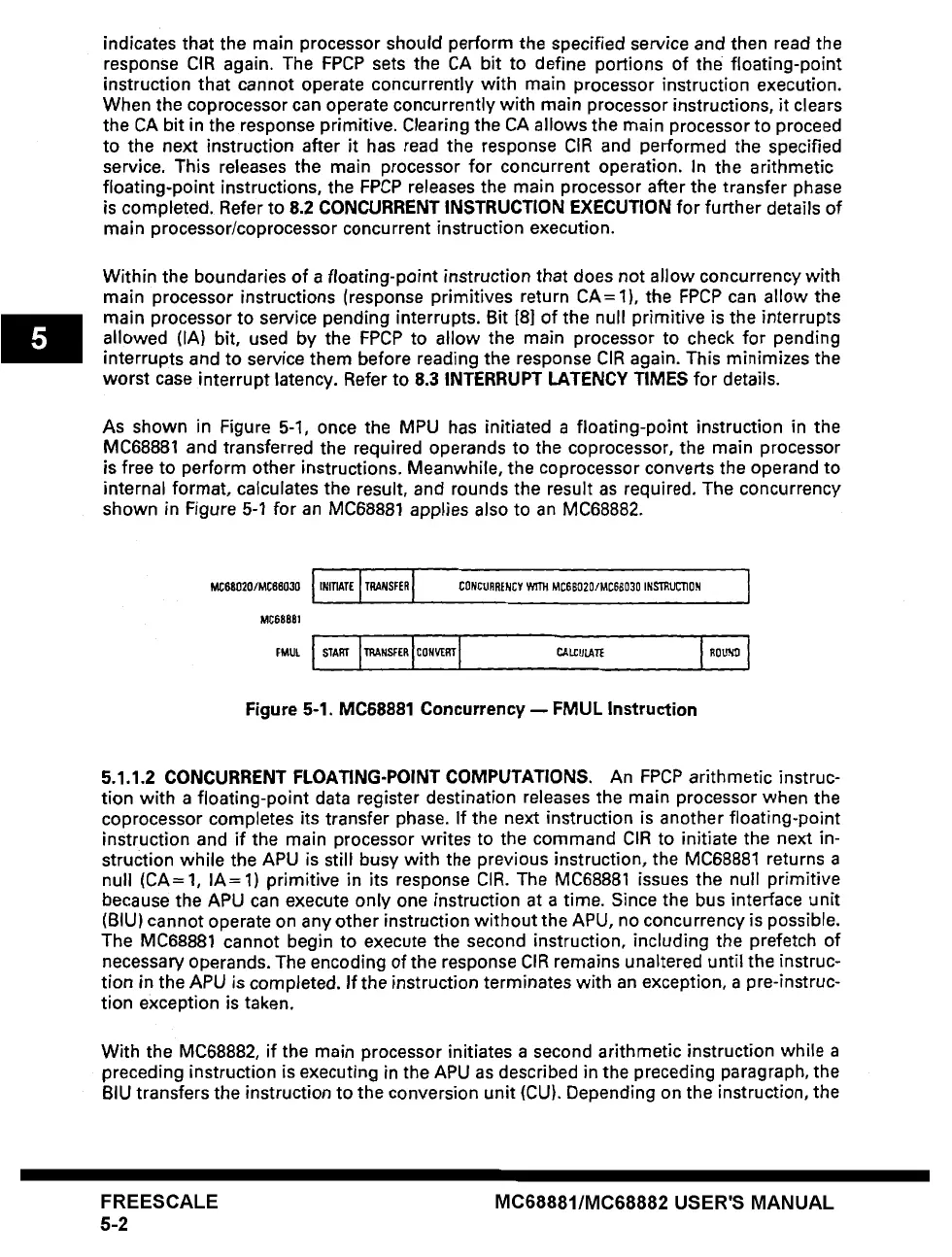

As shown in Figure 5-1, once the MPU has initiated a floating-point instruction in the

MC68881 and transferred the required operands to the coprocessor, the main processor

is free to perform other instructions. Meanwhile, the coprocessor converts the operand to

internal format, calculates the result, and rounds the result as required. The concurrency

shown in Figure 5-1 for an MC68881 applies also to an MC68882.

M:,,020/ :,8030 c0, U,.E,CY J

MC68881

FMUL ~

CALCULATE

Figure 5-1. MC68881 Concurrency -- FMUL Instruction

5.1.1.2 CONCURRENT FLOATING-POINT COMPUTATIONS. An FPCP arithmetic instruc-

tion with a floating-point data register destination releases the main processor when the

coprocessor completes its transfer phase. If the next instruction is another floating-point

instruction and if the main processor writes to the command CIR to initiate the next in-

struction while the APU is still busy with the previous instruction, the MC68881 returns a

null (CA=l, IA=I) primitive in its response CIR. The MC68881 issues the null primitive

because the APU can execute only one instruction at a time. Since the bus interface unit

(BIU) cannot operate on any other instruction without the APU, no concurrency is possible.

The MC68881 cannot begin to execute the second instruction, including the prefetch of

necessary operands. The encoding of the response CIR remains unaltered until the instruc-

tion in the APU is completed. If the instruction terminates with an exception, a pre-instruc-

tion exception is taken.

With the MC68882, if the main processor initiates a second arithmetic instruction while a

preceding instruction is executing in the APU as described in the preceding paragraph, the

BIU transfers the instruction to the conversion unit (CU}. Depending on the instruction, the

FREESCALE

5-2

MC68881/MC68882 USER'S MANUAL

Loading...

Loading...