effective address calculation and operand transfer times are different. Notice that the timing

prior to the start of the conversion operation is almost entirely dependent on the execution

characteristics of the main processor, while the timing for the rest of the instruction is

dependent solely on the FPCP. This distinction is useful when the execution timing for a

main processor other than the MC68020 or MC68030 is to be determined.

NOTE

The term "not normalized" is used frequently in the following tables. This term

is used where conditions allow the input of a denormalized or unnormalized

number, and the term

"denormalized"

is used where only a denormalized input

is possible. Refer to 3.2.2 Denormalized Numbers for a description of the denor-

malized and unnormalized data types.

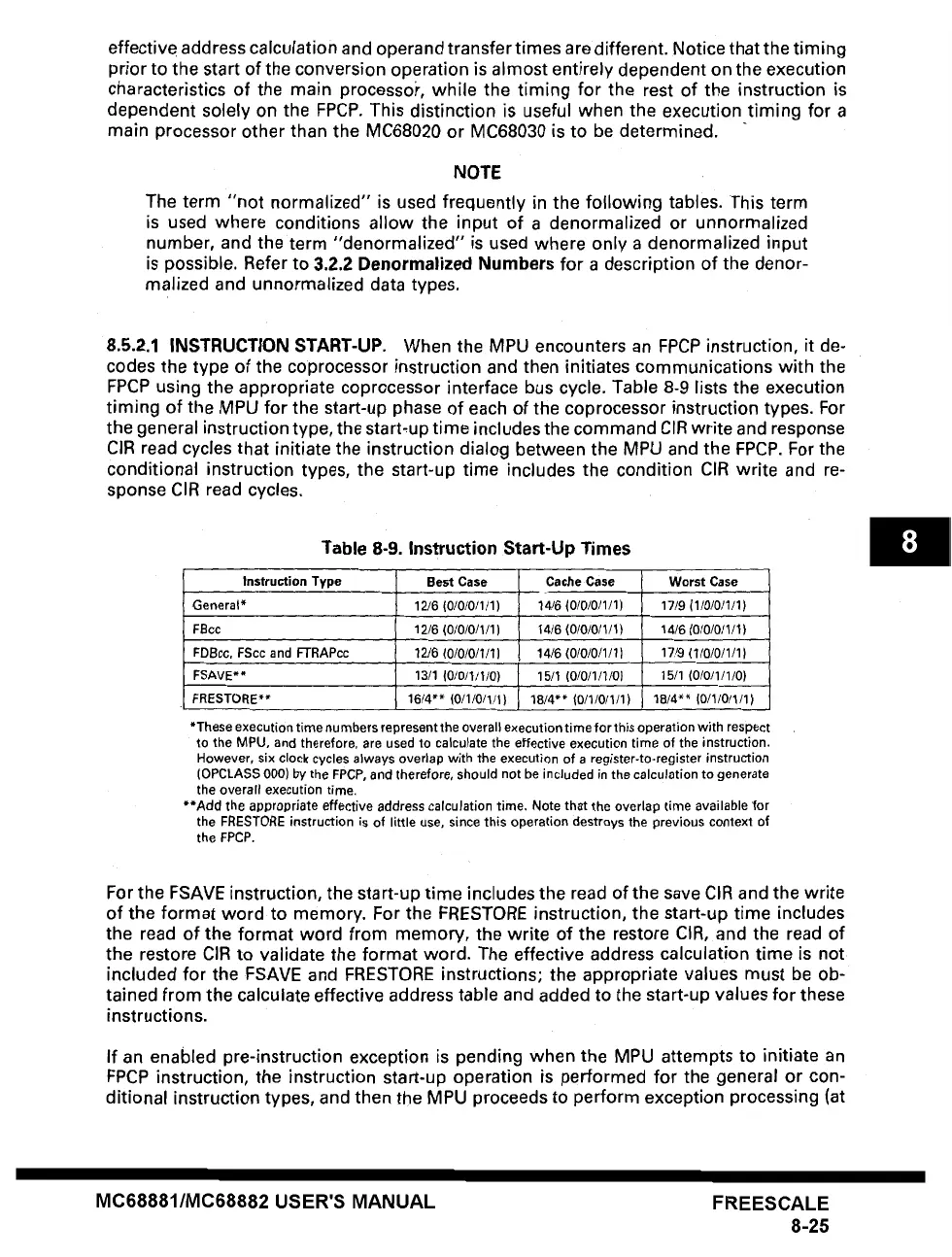

8.5.2.1 INSTRUCTION START-UP. When the MPU encounters an FPCP instruction, it de-

codes the type of the coprocessor instruction and then initiates communications with the

FPCP using the appropriate coprocessor interface bus cycle. Table 8-9 lists the execution

timing of the MPU for the start-up phase of each of the coprocessor instruction types. For

the general instruction type, the start,up time includes the command CIR write and response

CIR read cycles that initiate the instruction dialog between the MPU and the FPCP. For the

conditional instruction types, the start-up time includes the condition CIR write and re-

sponse CIR read cycles.

Table 8-9. Instruction Start-Up Times

Instruction Type Best Case Cache Case Worst Case

General* 12/6

(0101011/1)

14/6

(010101111)

17/9

{1101011fl}

FBcc 12/6

(0/0/0/1/1)

14/6

(0/0/0/1/1)

14/6 (0/0/0/1/I)

FDBcc, FScc and FTRAPcc 12/6 (0/0/0/1/1) 14/6 (0/0/0/1/1) 17/9

(1/01011/1)

FSAVE** 13/1

(010111110)

15/1 (0/0/1/1/0} 15/1 (0/0/1/1/0)

FRESTORE** 16/4"* (0/1/0/1/1} 18/4"*

(0Ilf0/1/1)

18/4 ** (0/1/0/1/1)

*These execution time numbers represent the overall execution time for this operation with respect

to the MPU, and therefore, are used to calculate the effective execution time of the instruction.

However, six clock cycles always overlap with the execution of a register-to-register instruction

(OPCLASS 000) by the FPCP, and therefore, should not be included in the calculation to generate

the overall execution time.

**Add the appropriate effective address

calculation

time. Note that the overlap time available for

the FRESTORE instruction is of little use, since this operation destroys the previous context of

the FPCP.

For the FSAVE instruction, the start-up time includes the read of the save CIR and the write

of the format word to memory. For the FRESTORE instruction, the start-up time includes

the read of the format word from memory, the write of the restore CIR, and the read of

the restore CIR to validate the format word. The effective address calculation time is not

included for the FSAVE and FRESTORE instructions; the appropriate values must be ob-

tained from the calculate effective address table and added to the start-up values for these

instructions.

If an enabled pre-instruction exception is pending when the MPU attempts to initiate an

FPCP instruction, the instruction start-up operation is performed for the general or con-

ditional instruction types, and then the MPU proceeds to perform exception processing (at

MC68881/MC68882 USER'S MANUAL

FREESCALE

8-25

Loading...

Loading...