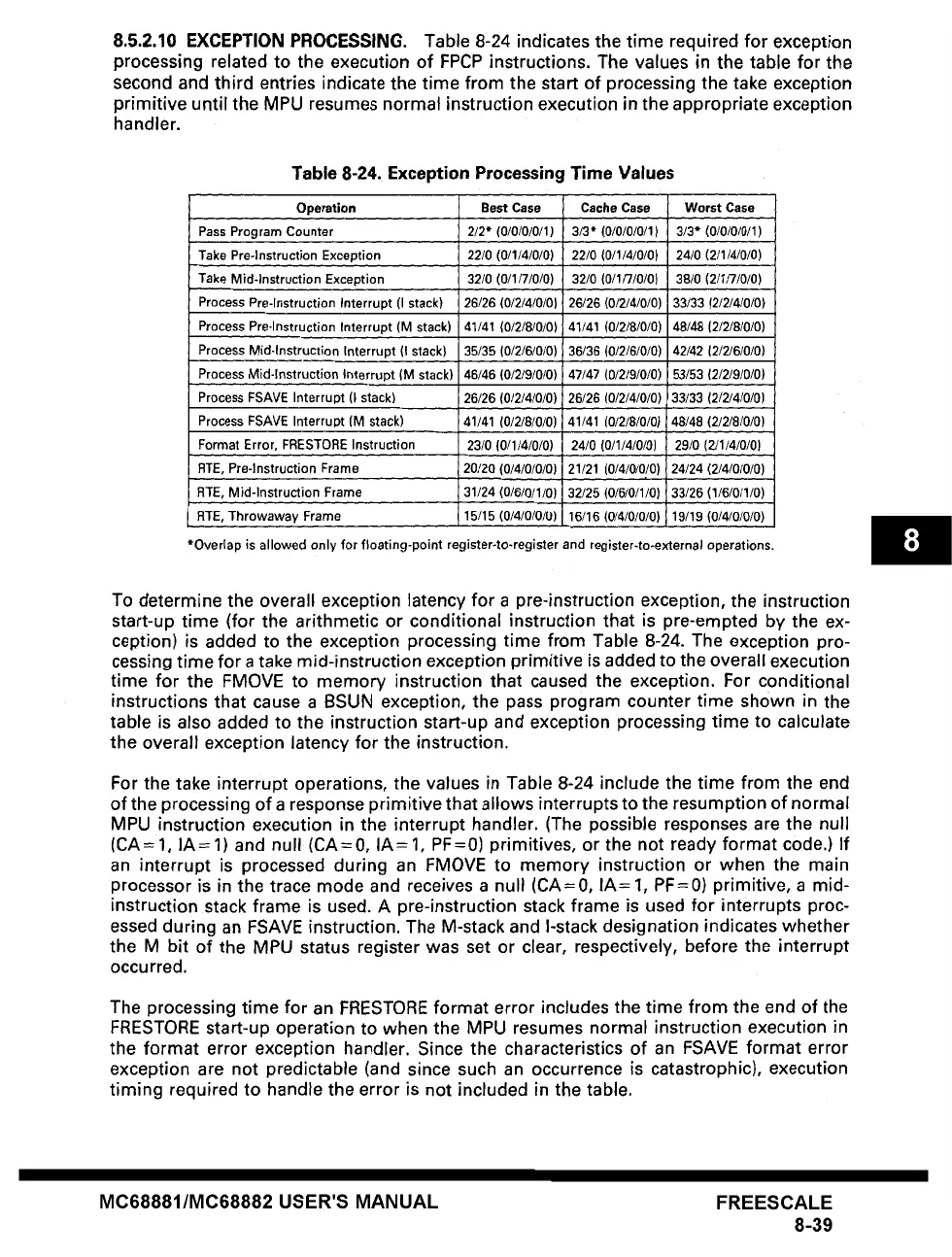

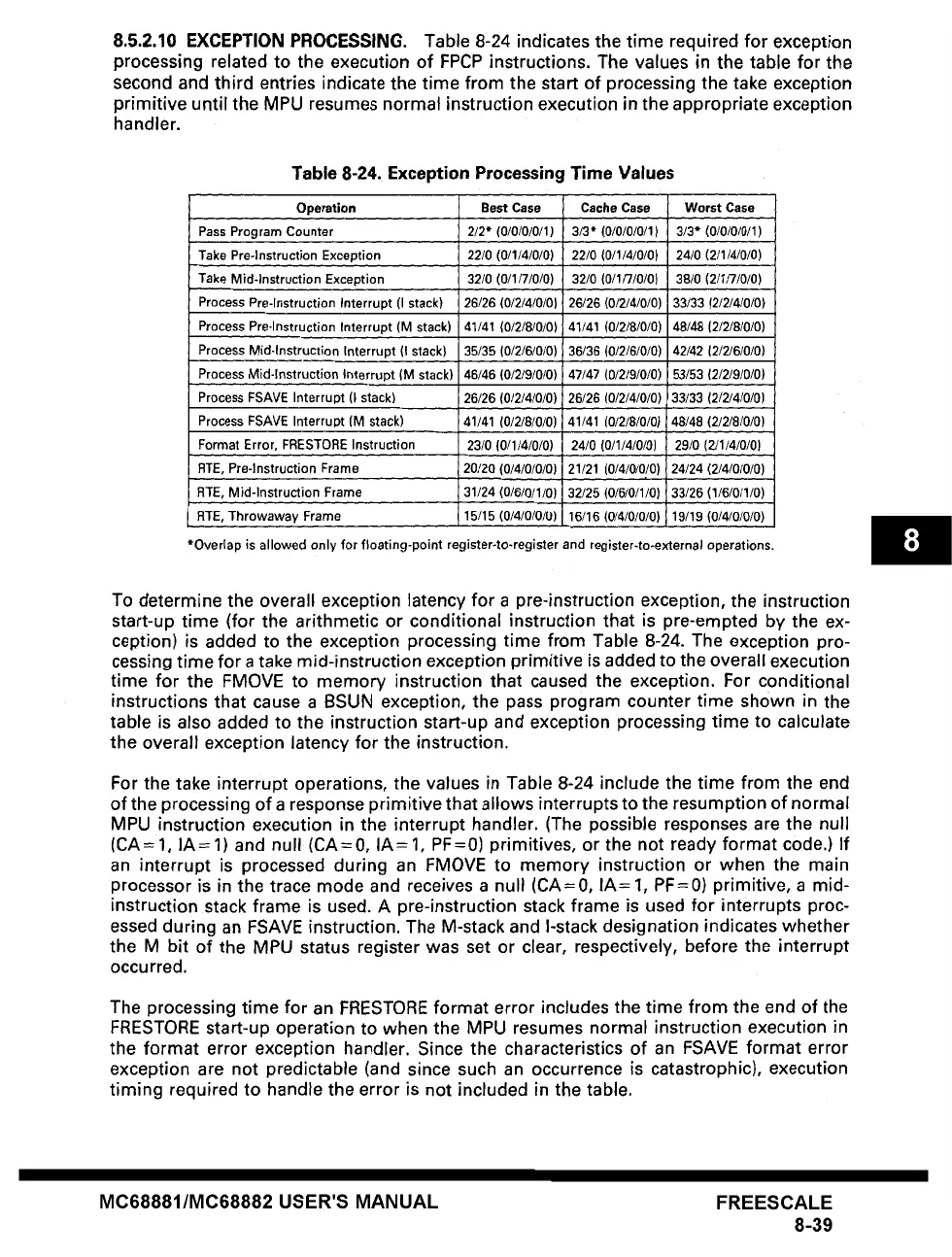

8.5.2.10 EXCEPTION PROCESSING. Table 8-24 indicates the time required for exception

processing related to the execution of FPCP instructions, The values in the table for the

second and third entries indicate the time from the start of processing the take exception

primitive until the MPU resumes normal instruction execution in the appropriate exception

handler.

Table 8-24. Exception Processing Time Values

Operation Best Case

Pass Program Counter 2/2* (0/0/0/0/1)

Take Pre-lnstruction Exception 22/0 (0/1/4/0/0)

Take Mid-instruction Exception 3210

(0/1/7/0/0)

Cache Case Worst Case

3/3* (0/0/0/0/1) 3/3*

(0/0/010/1)

22/0 (0ll/4/0/0) 24/0

(211/410/0)

32/0 (0/1/7/0/0) 38/0 (2/1/7/0/0)

Process Pre-lnstruction Interrupt (I stack) 26/26 (0/2/4/0/0) 26/26

(0/2/4/0t0)

33/33 (2/2/4/0/0)

Process Pre-lnstruction Interrupt (M stack) 41/41

(0/2/810/0)

41/41

(012/81010)

48148

(2/218/0/0)

Process Mid-Instruction Interrupt (I stack) 35/35 (0/2f6/0/0) 36•36

(0/2t6/0/0)

42/42 12/2/6/0f0)

Process Mid-Instruction Interrupt (M stack) I 46•46

(012f9t0f0)

47147

(0/219/0/0)

53•53 (2/2f9/0/0)

I

Process FSAVE Interrupt (I stack) i 26/26

(012/410/0)

26/25

(0t2/4/0/0)

33/33

(2/2/4/0/0)

Process FSAVE Interrupt (M stack) ,41/41 (0/21810/0] 41/41 (0/2/8/0/0) 48/48

(2/2/81010)

Format Error, FRESTORE Instruction 23/0 (0/1/4/0/0) 24/0 (0/1/4/0/0) 29/0 (2/1/4/010)

RTE, Pre-lnstruction Frame 20120 (0/4/0/0/0) 21/21

(0/4/01010)

24/24

(21410/0/0)

RTE, Mid-Instruction Frame '31/24

(0/6/011/0)

32•25

(0/6f0/110)

33/26 (1t6/011/0)

RTE, Throwaway Frame 15/15

(0f4/010/0)

16/16

(0/4/0/0f0)

19119 (0/4/0/0/0)

*Overlap is allowed only for floating-point register-to-register and register-to-external operations.

To determine the overall exception latency for a pre-instruction exception, the instruction

start-up time (for the arithmetic or conditional instruction that is pre-empted by the ex-

ception) is added to the exception processing time from Table 8-24. The exception pro-

cessing time for a take mid-instruction exception primitive is added to the overall execution

time for the FMOVE to memory instruction that caused the exception. For conditional

instructions that cause a BSUN exception, the pass program counter time shown in the

table is also added to the instruction start-up and exception processing time to calculate

the overall exception latency for the instruction.

For the take interrupt operations, the values in Table 8-24 include the time from the end

of the processing of a response primitive that allows interrupts to the resumption of normal

MPU instruction execution in the interrupt handler. (The possible responses are the null

(CA= 1, IA= 1) and null (CA=0, IA= 1, PF=0) primitives, or the not ready format code.) If

an interrupt is processed during an FMOVE to memory instruction or when the main

processor is in the trace mode and receives a null (CA=0, IA= 1, PF=0) primitive, a mid-

instruction stack frame is used. A pre-instruction stack frame is used for interrupts proc-

essed during an FSAVE instruction. The M-stack and I-stack designation indicates whether

the M bit of the MPU status register was set or clear, respectively, before the interrupt

occurred.

The processing time for an FRESTORE format error includes the time from the end of the

FRESTORE start-up operation to when the MPU resumes normal instruction execution in

the format error exception handler. Since the characteristics of an FSAVE format error

exception are not predictable (and since such an occurrence is catastrophic), execution

timing required to handle the error is not included in the table.

MC68881/MC68882 USER'S MANUAL

FREESCALE

8-39

Loading...

Loading...