SECTION 2

PROGRAMMING MODEL

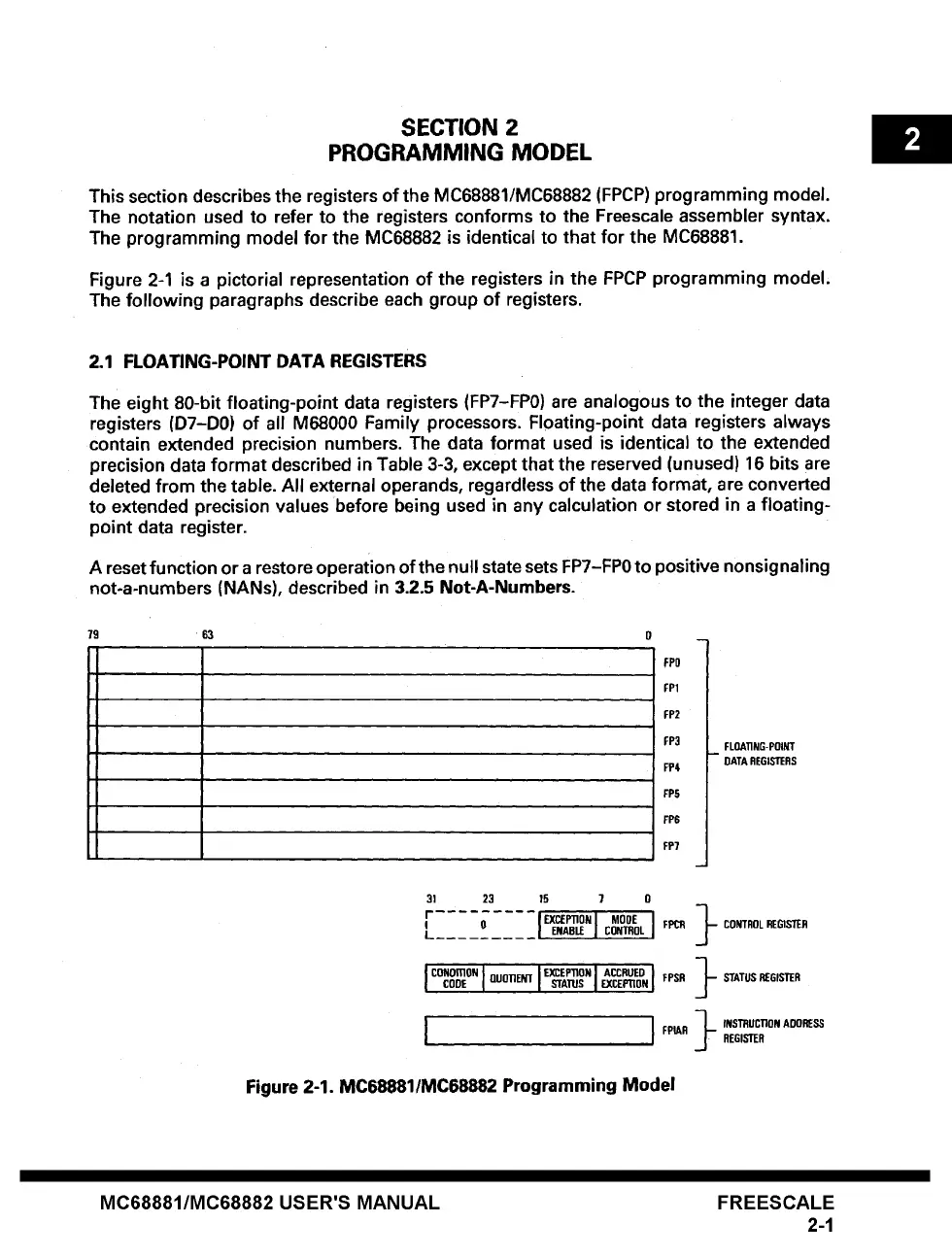

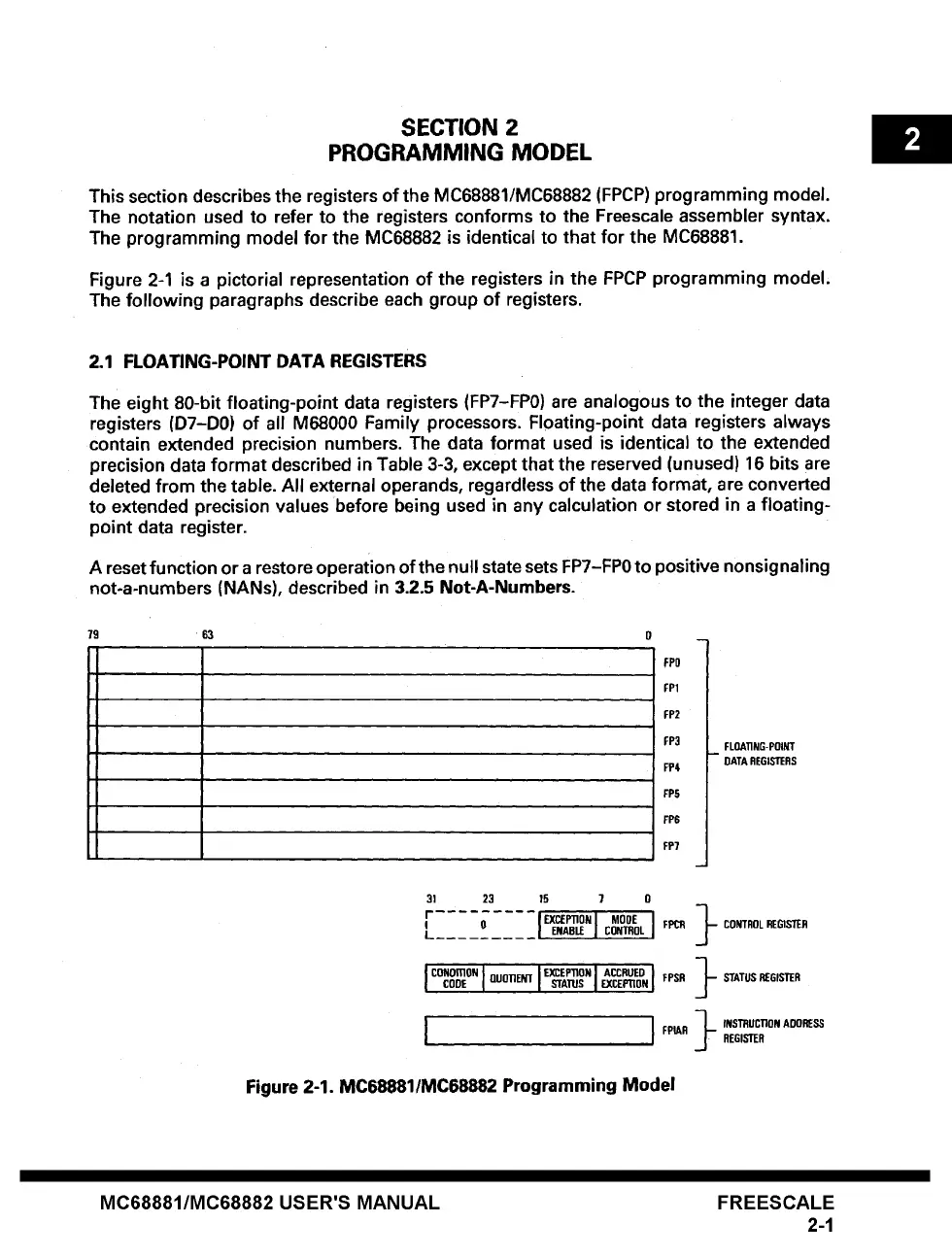

This section describes the registers of the MC68881/MC68882 (FPCP) programming model.

The notation used to refer to the registers conforms to the Freescale assembler syntax.

The programming model for the MC68882 is identical to that for the MC68881.

Figure 2-1 is a pictorial representation of the registers in the FPCP programming model,

The following paragraphs describe each group of registers.

2.1 FLOATING-POINT DATA REGISTERS

The eight 80-bit floating-point data registers (FP7-FP0) are analogous to the integer data

registers (D7-D0) of all M68000 Family processors. Floating-point data registers always

contain extended precision numbers. The data format used is identical to the extended

precision data format described in Table 3-3, except that the reserved (unused) 16 bits are

deleted from the table. All external operands, regardless of the data format, are converted

to extended precision values before being used in any calculation or stored in a floating-

point data register.

A reset function or a restore operation of the null state sets FP7-FP0 to positive nonsignaling

not-a-numbers (NANs), described in 3.2.5 Not-A-Numbers.

79 63

FPO

FP1

FP2

FP3

FP4

FPS

FP6

FP7

FLOATING-P01NT

DATA REGISTERS

31 23 15 7 O

'" .... ~ .... 'EXCEPTION'MODE I FPCR ~._ CONTROL REGISTER

u ] ENABLE ]CONTROL

EXCE~D,,I AC~RUEO

I

I o.omoN

CODE I QUOTIENT STATUS ~ EXCEP~O~I I FPSR STATUS REGISTER

I I - - 7 'NsT 'cTI°'°oRE s

t-~.AK .j.-- REGISTER

Figure 2-1. MC68881/MC68882 Programming Model

MC68881/MC68882 USER'S MANUAL FREESCALE

2-1

Loading...

Loading...