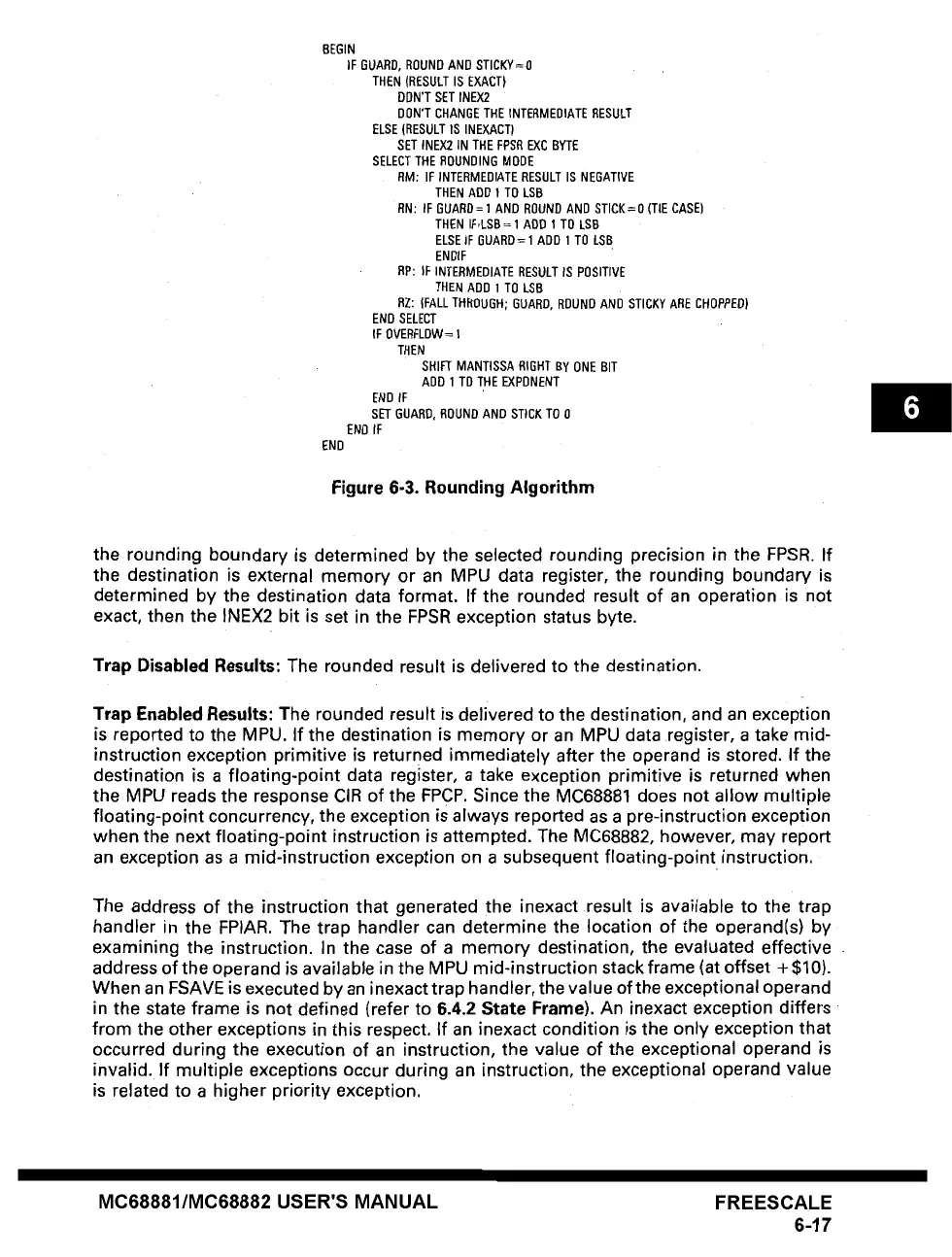

BEGIN

IF GUARD, ROUND AND STICKY=O

THEN (RESULT IS EXACT)

DON'T SET INEX2

DON'T CHANGE THE INTERMEDIATE RESULT

ELSE (RESULT IS INEXACT)

SET INEX2 IN TIlE EPSR EXC BYTE

SELECT THE ROUNDING MODE

RM: IF INTERMEDIATE RESULT IS NEGATIVE

THEN ADD 1 TO LSB

RN: IF GUARD = 1 AND ROUND AND STICK=O (TIE CASE)

THEN IF,LSB = 1 ADD I TO LSB

ELSE IF GUARD = 1 ADD 1 TO LSB

ENDIF

BP: IF INTERMEDIATE RESULT IS POSITIVE

THEN ADD I TO LSB

RZ: (FALL THROUGH; GUARD, ROUND AND STICKY ARE CHOPPED)

END SELECT

IF OVERFLOW = 1

THEN

SHIFT MANTISSA RIGHT BY ONE BIT

ADD 1 TO THE EXPONENT

END

IF

SET GUABD, ROUND AND STICK TO 0

END IF

ENO

Figure 6-3. Rounding Algorithm

the rounding boundary is determined by the selected rounding precision in the FPSR. If

the destination is external memory or an MPU data register, the rounding boundary is

determined by the destination data format. If the rounded result of an operation is not

exact, then the INEX2 bit is set in the FPSR exception status byte.

Trap

Disabled Results:

The rounded result is delivered to the destination.

Trap Enabled Results:

The rounded result is delivered to the destination, and an exception

is reported to the MPU. If the destination is memory or an MPU data register, a take mid-

instruction exception primitive is returned immediately after the operand is stored. If the

destination is a floating-point data register, a take exception primitive is returned when

the MPU reads the response CIR of the FPCP. Since the MC68881 does not allow multiple

floating-point concurrency, the exception is always reported as a pre-instruction exception

when the next floating-point instruction is attempted. The MC68882, however, may report

an exception as a mid-instruction exception on a subsequent floating-point instruction.

The address of the instruction that generated the inexact result is available to the trap

handier in the FPIAR. The trap handler can determine the location of the operand(s) by

examining the instruction. In the case of a memory destination, the evaluated effective

address of the operand is available in the MPU mid-instruction stack frame (at offset + $10).

When an FSAVE is executed by an inexact trap handler, the value of the exceptional operand

in the state frame is not defined (refer to 6.4.2

State Frame).

An inexact exception differs

from the other exceptions in this respect. If an inexact condition is the only exception that

occurred during the execution of an instruction, the value of the exceptional operand is

invalid. If multiple exceptions occur during an instruction, the exceptional operand value

is related to a higher priority exception.

MC68881/MC68882 USER'S MANUAL

FREESCALE

6-17

Loading...

Loading...