4

floating-point values so that all machines conforming to the standard produce the same

results for an operation. The operation must meet the following conditions:

1. Same input values,

2. Same rounding mode, and

3. Same precision.

The IEEE standard specifies not only the format of data items, but also defines:

1. The maximum allowable error that may be introduced during a calculation, and

2. The manner in which rounding of the result is performed.

However, the iEEE specification defines only the operation of some of the instructions

supported by the FPCP; those not specified by the IEEE standard are described in detail

in the following paragraphs. The following paragraphs discuss the accuracy of the calcu-

lations performed by the FPCP, grouping them as follows:

1. The IEEE specified operations and nontranscendental functions,

2. The transcendental functions, and

3. The IEEE specified conversions between binary and decimal real formats.

4.3.1 Arithmetic Instructions

The /EEE Specification for Binary Floating-Point Arithmetic specifies that the following

operations must be supported for each data format: add, subtract, multiply, divide, re-

mainder, square root, integer part, and compare. Conversions between the various data

formats are also required. In addition to these arithmetic functions, the FPCP also supports

the nontranscendental operations of: absolute value, get exponent, get mantissa, negate,

modulo remainder, scale exponent, and test. Since the IEEE specification defines the error

bounds to which all calculations are performed, the result obtained by any conforming

machine can be predicted exactly for a particular precision and rounding mode. The error

bound defined by the IEEE specification is one-half unit in the last place of the destination

data format in the round-to-nearest mode and one unit in the last place in the other rounding

modes.

The FPCP performs all calculations using a 67-bit mantissa for the intermediate results.

The three bits beyond the precision of the extended format allow the FPCP to perform all

calculations as if to infinite precision and then round the result to the desired precision

before storing it in the destination. By performing calculations in this manner, the final

result is always correct for the specified destination data format before rounding is per-

formed (unless an overflow or underflow error occurs). The specified rounding operation

then produces a number that is as close as possible to the infinitely precise intermediate

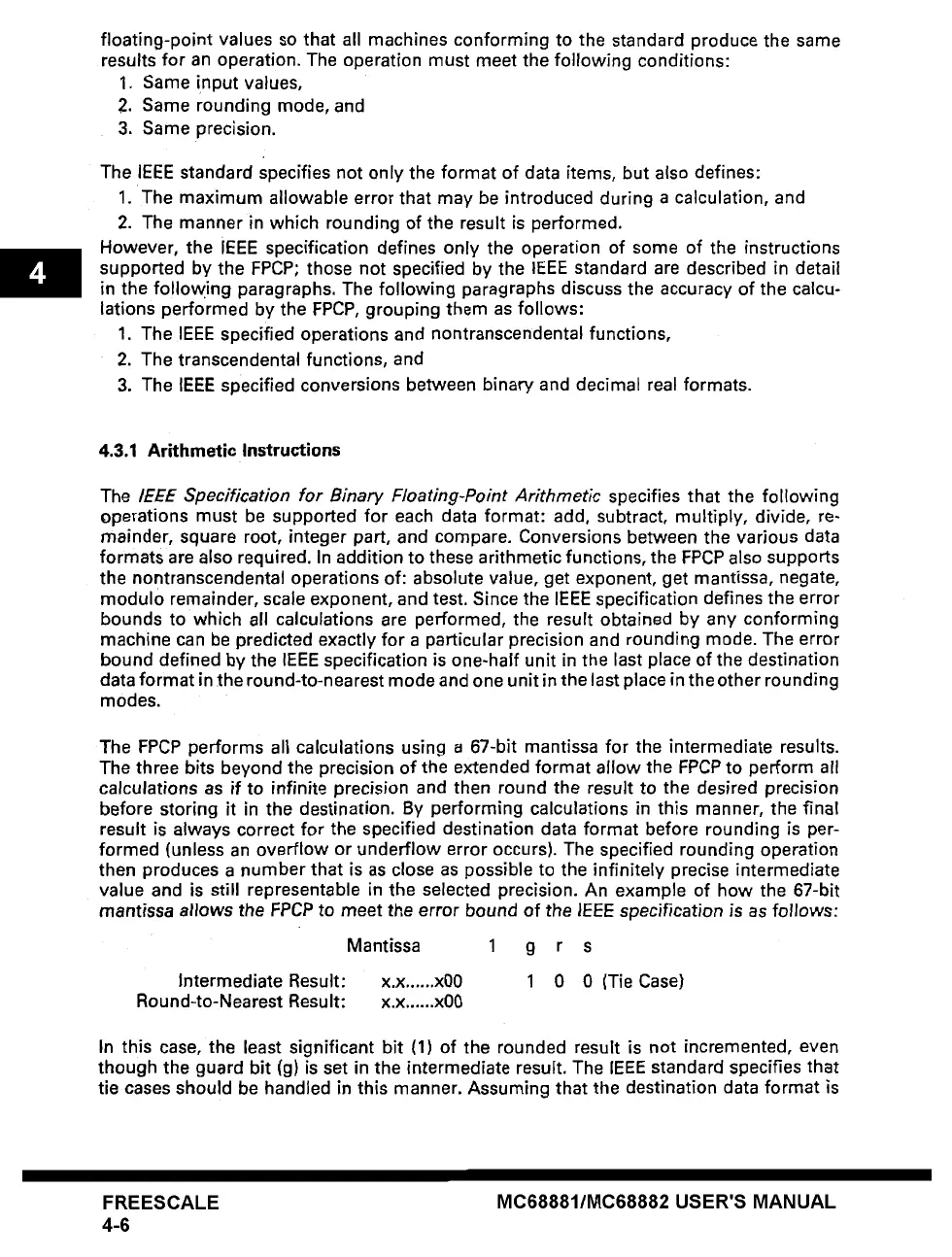

value and is still representable in the selected precision. An example of how the 67-bit

mantissa

allows the FPCP to meet the error bound of the JEEE speci~cation is as follows:

Mantissa 1 g r s

Intermediate Result: x.x ...... x00 1 0 0 (Tie Case)

Round-to-Nearest Result: x.x ...... x00

In this case, the least significant bit (1) of the rounded result is not incremented, even

though the guard bit (g) is set in the intermediate result. The IEEE standard specifies that

tie cases should be handled in this manner. Assuming that the destination data format is

FREESCALE

4-6

MC68881/MC68882 USER'S MANUAL

Loading...

Loading...