that exception class is disabled. (A user write operation to the status register, which sets

a bit in the EXC byte, does not cause a trap to be taken regardless of the value in the

ENABLE byte.)

Note that the bits in the status EXC byte and control ENABLE byte are in the same bit

positions within each byte. The eight floating-point exception classes are described in

greater detail in SECTION 6 EXCEPTION PROCESSING.

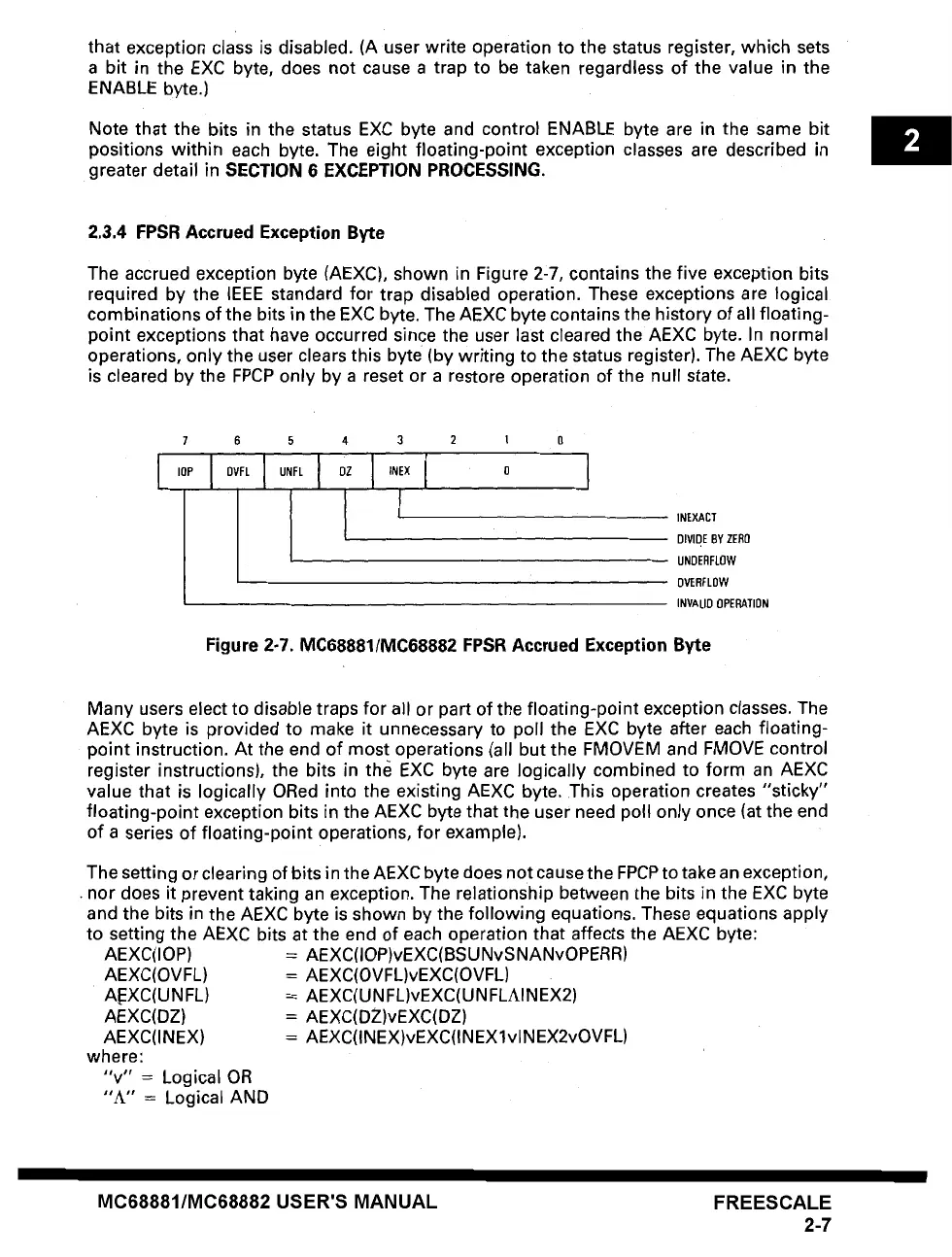

2.3.4 FPSR Accrued Exception Byte

The accrued exception byte (AEXC), shown in Figure 2-7, contains the five exception bits

required by the IEEE standard for trap disabled operation. These exceptions are logical

combinations of the bits in the EXC byte. The AEXC byte contains the history of all floating-

point exceptions that have occurred since the user last cleared the AEXC byte. In normal

operations, only the user clears this byte (by writing to the status register). The AEXC byte

is cleared by the FPCP only by a reset or a restore operation of the null state.

I II

,[o,

III

FLI

3 2 1 O

INEXACT

DIVIDE BY ZERO

UNDERFLOW

OVERFLOW

INVALID OPERATION

Figure 2-7. MC68881/MC68882 FPSR Accrued Exception Byte

Many users elect to disable traps for all or part of the floating-point exception classes. The

AEXC byte is provided to make it unnecessary to poll the EXC byte after each floating-

point instruction. At the end of most operations (all but the FMOVEM and FMOVE control

register instructions), the bits in the EXC byte are logically combined to form an AEXC

value that is logically ORed into the existing AEXC byte. This operation creates "sticky"

floating-point exception bits in the AEXC byte that the user need poll only once (at the end

of a series of floating-point operations, for example).

The setting or clearing of bits in the AEXC byte does not cause the FPCP to take an exception,

nor does it prevent taking an exception. The relationship between the bits in the EXC byte

and the bits in the AEXC byte is shown by the following equations. These equations apply

to setting the AEXC bits at the end of each operation that affects the AEXC byte:

AEXC(IOP)

AEXC(OVFL)

AI~XC(UNFL)

AEXC(DZ)

AEXC(INEX)

where:

"v"

= Logical OR

"A" = Logical AND

= AEXC(IOP)vEXC(BSU NvSNANvOPERR)

= AEXC(OVFL)vEXC(OVFL)

= AEXC(U NFL)vEXC(UNFLAINEX2)

= AEXC(DZ)vEXC(DZ)

= AEXC(INEX)vEXC(INEXlvlNEX2vOVFL)

MC68881/MC68882 USER'S MANUAL FREESCALE

2-7

Loading...

Loading...