8

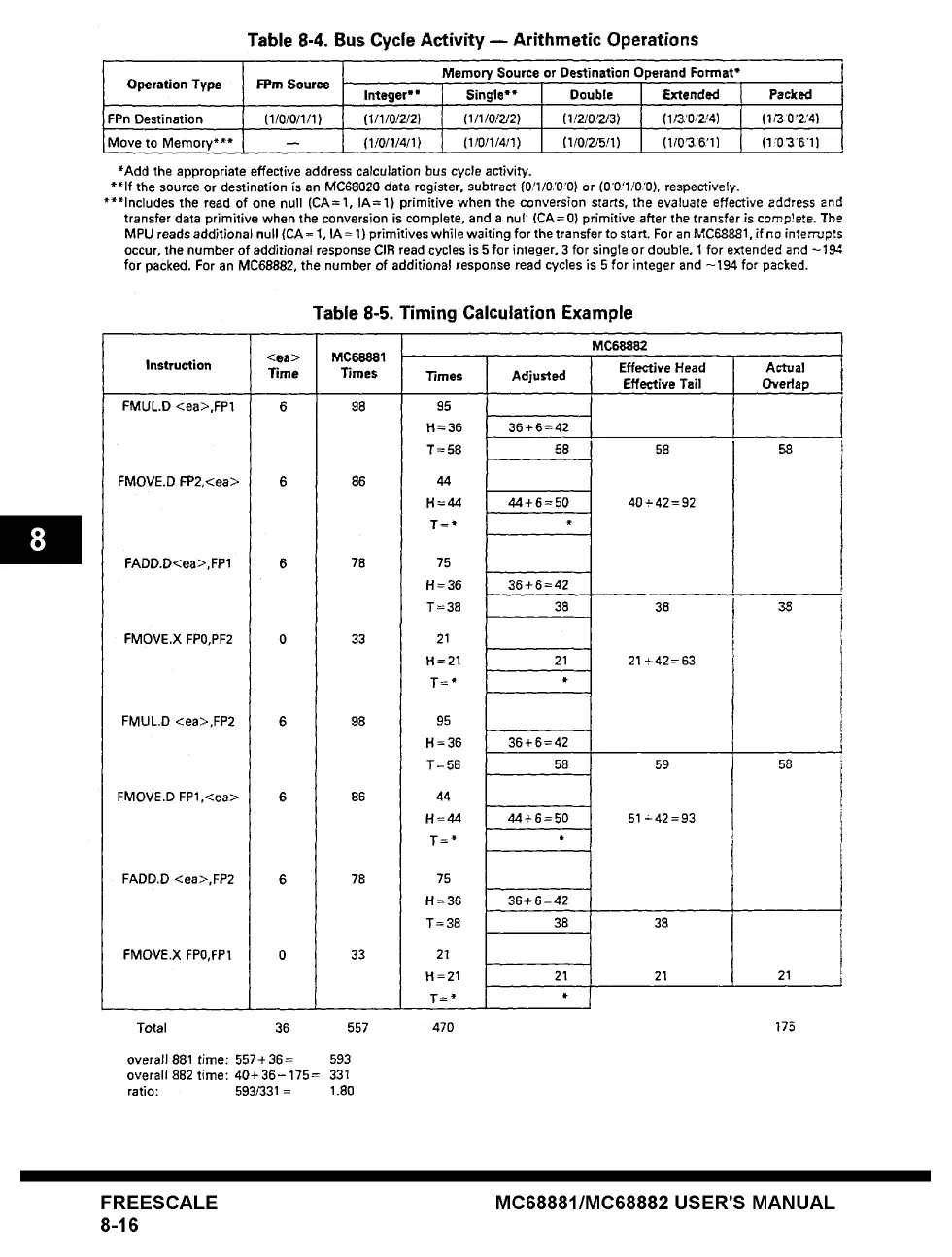

Table 8-4. Bus Cycle Activity -- Arithmetic Operations

Memory Source or Destination Operand Format*

Operation Type FPm Source

Integer** Single** Double Extended Packed

FPn Destination (1/0/0/1/1)

(1/1/0,/2/2)

(1/1/0/2_/2) (1/2/0/2/3) (1/3'0"2'4) (1;3 0'Z'4)

Move to Memory*** -- (110111411) (110111411) (1/0/2/5!1) (1/03'6'1) (1;0"3'6'1)

*Add the appropriate effective address calculation bus cycle activity.

**If the source or destination is an MC68020 data register, subtract l'0/1/0/0'0) or (0;0fl/0'O). respectively.

***Includes the read of one null (CA= 1, IA= 1) primitive when the conversion

starts,

the

evaluate

effective address and

transfer data primitive when the conversion is complete, and a null (CA= O) primitive after the transfer is comp.~ete. The

MPU reads additional null (CA = 1, IA = 1) primitives while waiting for the transfer to start. For an MC62,881, if no interrupts

occur, the number of

additional

response CIR read cycles is 5 for integer, 3 for singTe or double, 1 for extended and -194

for packed. For an MC68882, the number of additional response read cycles is 5 for integer and -194 for packed.

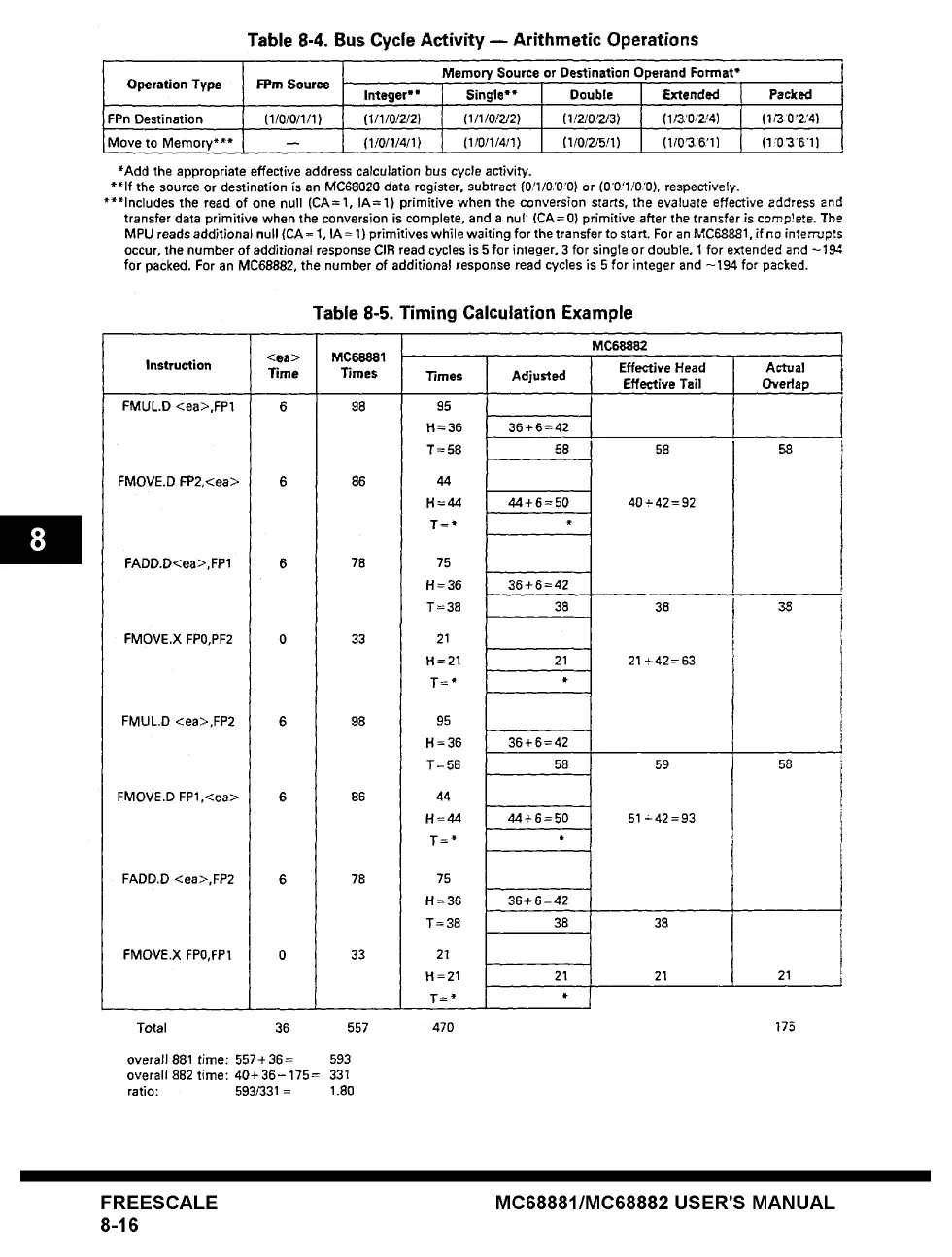

Instruction <ea>

Time

FMUL.D <ea>,FP1 6

Table 8-5. Timing Calculation Example

MC68882

MC68881

Times Times

Adjusted Effective Head Actual

Effective Tail OveHap

98

FMOVE.D FP2,<ea> 6 86

FADD.D<ea>,FP1 6 78

FMOVE.X FP0,PF2 0 33

FMUL.D <ea~>,FP2 6 98

FMOVE.D FPl,<ea> 6 86

FADD.D <ea>,FP2 6 78

FMOVE.X FP0,FP1 0 33

95

H=36

T= 58

44

H=44

m=*

75

H=36

T=38

21

H=21

T=*

95

H =36

T=58

44

H=44

T=*

75

H=36

T=36

21

H =21

m =*

Total 36 557 470

overall 881

time:

557+36= 593

overall 882 time: 40+36-175= 331

ratio: 593/331 = 1.80

36+6=42

58

44+6=50

36+6=42

38

21

36+6=42

58

44+6=50

36+6=42

38

21

58

40+42=92

38

21 + 42 = 63

59

51 "-42=93

38

21

I

58

38

58

I

t

21

175

FREESCALE

8-16

MC68881/MC68882 USER'S MANUAL

Loading...

Loading...