8

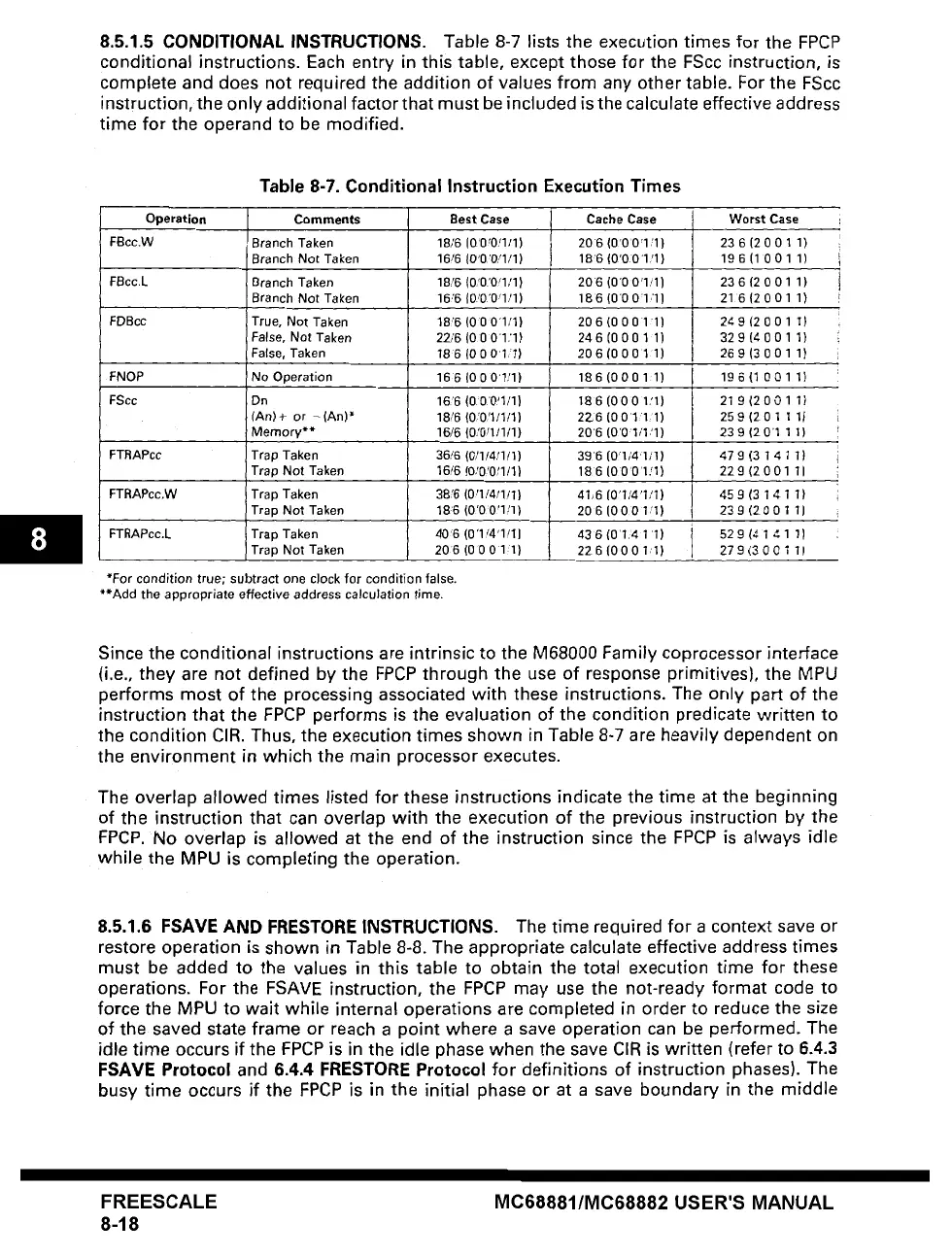

8.5.1.5 CONDITIONAL INSTRUCTIONS. Table 8-7 lists the execution times for the FPCP

conditional instructions. Each entry in this table, except those for the FScc instruction, is

complete and does not required the addition of values from any other table. For the FScc

instruction, the only additional factor that must be included is the calculate effective address

time for the operand to be modified.

Table 8-7. Conditional Instruction Execution Times

Operation Comments Best

Case

Cache Case Worst Case

FBcc.W Branch Taken 18J610 0'0.'1/1) 206 (0'O0'1'1} 23 6 {2 0 0 1 1)

'Branch Not Taken 1616 [0'0'O'111) 186

(0'00'1/1)

19 6 (1 0 0 1 1)

FBcc.L Branch Taken 18/6 {0'0'0~1/1) 206 (0'0 0'1.~1) 23 6 {20 0 1 1)

Branch Not Taken 16.'6 [0'0'0'111) 186 (0'0 0'1,'1) 21 6 (2 0 0 1 1)

FDBcc True, Not Taken 18'6 (00 0'1/1) 20 6 (0 0 01 '1) 24 9 (2 0 0 1 I)

False, Not Taken 22/6 (0 0 0'1.'1) 24 6 (0 0 0 1 1) 329 (4 0 0 1 1)

False, Taken 186 (0 0 01'1) 20 6 (0 0 01 1) 26 9 (3 0 0 1 1)

FNOP No Operation 166(000'1"1) 1 186(00011) 196(10011)

FScc

Dn 16'6 (0 0'0'1/1) 18 6 (0 0 0 1.'1) 21 9 (2 0 0 1 1}

(An) + or - (An)* 18'6 (0'0'1/1/1) 22.6 (0 0'1 1.1) 259 (20 1 1 1)

Memory** 16/6 (0/0/1/1/1) 20'6

(0'0'1/1.'1)

23 9 (20'1 1 1)

FTRAPcc Trap Taken 36/6

(0/lf4.'1/1)

39'6

(0'1,'4'1/1)

47 9 (3 I 4 1 1)

Trap Not Taken 16f6 (0,'0'0'1/1) 18 6 (0 0'0rlJl) 229 (2 0 0111

FTRAPcc.W Trap Taken 38'6 (0'1/4/lq) 41,6 (0'114'I/1) 45 9 (3 1 4 1 1)

Trap Not Taken 18,'6 (0'0 0'1/1) 20 6 (0 00 1'1) 239 (20 0 1 1]

FTRAPcc.L Trap Taken 40 6 (0'1~4'1~11 43 6 (0 14 1 1) 529 (4 1 4 1 1)

Trap Not Taken 206(00011) 226{00011) 279(300111

*For condition true; subtract one clock for condition false.

**Add the appropriate

effective

address

calculation

time.

Since the conditional instructions are intrinsic to the M68000 Family coprocessor interface

(i.e., they are not defined by the FPCP through the use of response primitives), the MPU

performs most of the processing associated with these instructions. The only part of the

instruction that the FPCP performs is the evaluation of the condition predicate written to

the condition CIR. Thus, the execution times shown in Table 8-7 are heavily dependent on

the environment in which the main processor executes.

The overlap allowed times listed for these instructions indicate the time at the beginning

of the instruction that can overlap with the execution of the previous instruction by the

FPCP. No overlap is allowed at the end of the instruction since the FPCP is always idle

while the MPU is completing the operation.

8.5.1.6 FSAVE AND FRESTORE INSTRUCTIONS. The time required for a context save or

restore operation is shown in Table 8-8. The appropriate calculate effective address times

must be added to the values in this table to obtain the total execution time for these

operations. For the FSAVE instruction, the FPCP may use the not-ready format code to

force the MPU to wait while internal operations are completed in order to reduce the size

of the saved state frame or reach a point where a save operation can be performed. The

idle time occurs if the FPCP is in the idle phase when the save CIR is written (refer to 6.4.3

FSAVE Protocol and 6.4.4 FRESTORE Protocol for definitions of instruction phases). The

busy time occurs if the FPCP is in the initial phase or at a save boundary in the middle

FREESCALE

8-18

MC68881/MC68882 USER'S MANUAL

Loading...

Loading...