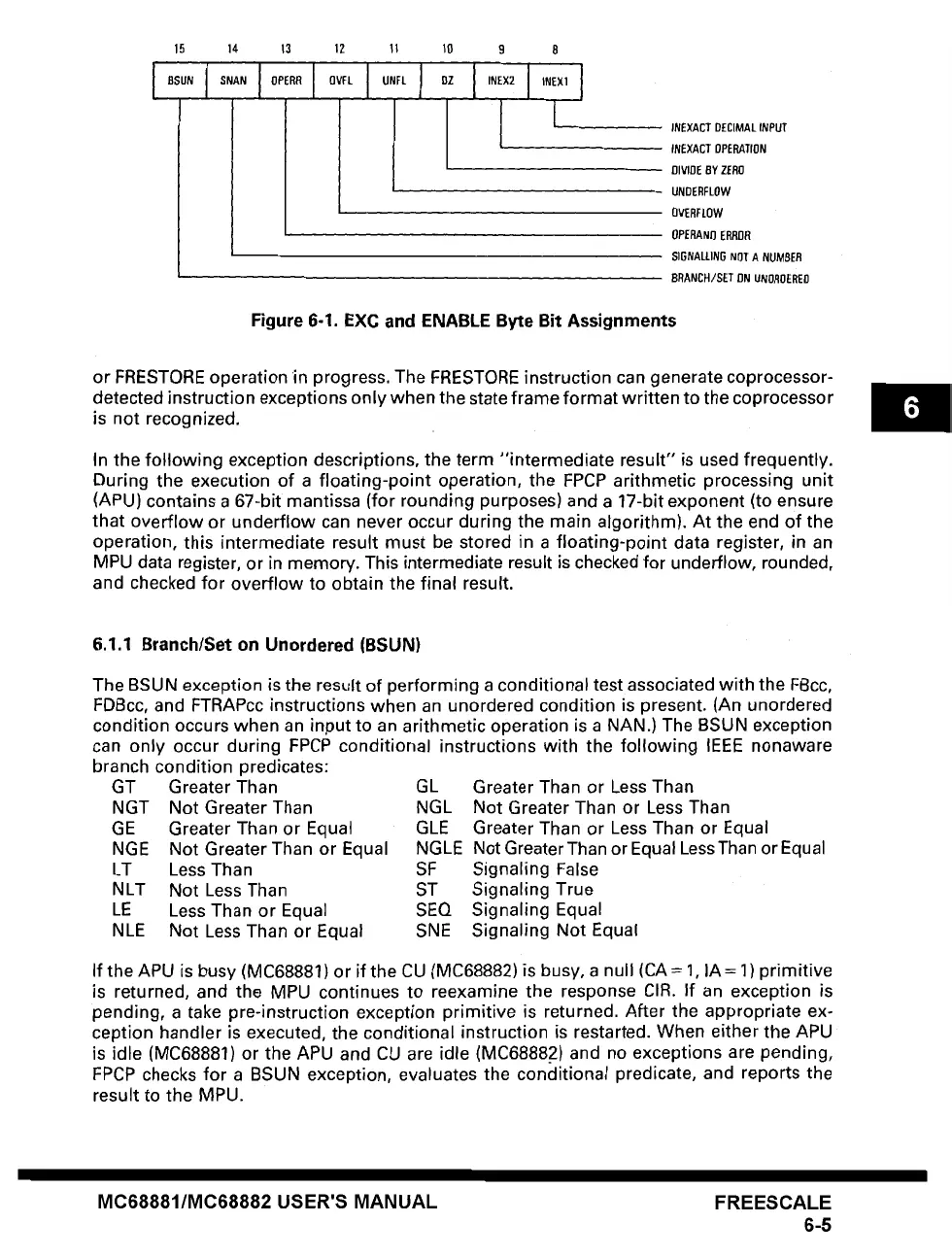

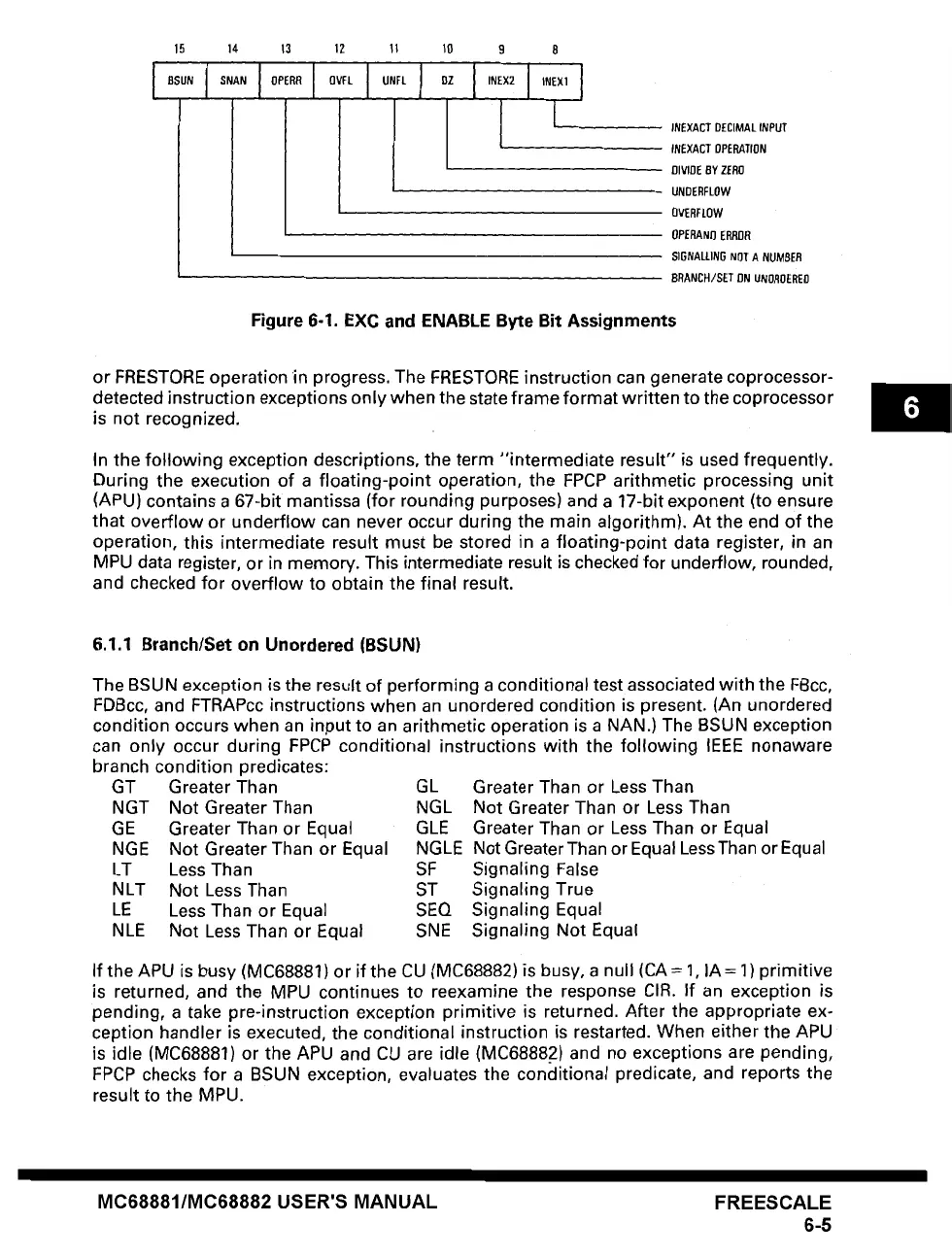

15 14 13 12 11 10 9 8

I I l

I l INEXACT DECIMAL INPUT

INEXACT OPERATION

BIVIOE 8Y ZERO

1 UNDERFLOW

i

i OVERFLOW

OPERANO ERROR

SIGNALLING NOT A NUMBER

BRANCH/SET ON UNORDERED

Figure 6-1. EXC and ENABLE Byte Bit Assignments

or FRESTORE operation in progress. The FRESTORE instruction can generate coprocessor-

detected instruction exceptions only when the state frame format written to the coprocessor

is not recognized.

In the following exception descriptions, the term "intermediate result" is used frequently.

During the execution of a floating-point operation, the FPCP arithmetic processing unit

(APU) contains a 67-bit mantissa (for rounding purposes) and a 17-bit exponent (to ensure

that overflow or underflow can never occur during the main algorithm). At the end of the

operation, this intermediate result must be stored in a floating-point data register, in an

MPU data register, or in memory. This intermediate result is checked for underflow, rounded,

and checked for overflow to obtain the final result.

6.1.1 Branch/Set on Unordered (BSUN)

The BSUN exception is the result of performing a conditional test associated with the FBcc,

FDBcc, and FTRAPcc instructions when an unordered condition is present. (An unordered

condition occurs when an input to an arithmetic operation is a NAN.) The BSUN exception

can only occur during FPCP conditional instructions with the following IEEE nonaware

branch condition predicates:

GT Greater Than

NGT Not Greater Than

GE Greater Than or Equal

NGE Not Greater Than or Equal

LT Less Than

NLT Not Less Than

LE Less Than or Equal

NLE Not Less Than or Equal

GL Greater Than or Less Than

NGL Not Greater Than or Less Than

GLE Greater Than or Less Than or Equal

NGLE Not GreaterThan or Equal Less Than or Equal

SF Signaling False

ST Signaling True

SEQ Signaling Equal

SNE Signaling Not Equal

If the APU is busy (MC68881) or if the CU (MC68882) is busy, a null (CA-- 1, IA= 1) primitive

is returned, and the MPU continues to reexamine the response CIR. If an exception is

pending, a take pre-instruction exception primitive is returned. After the appropriate ex-

ception handler is executed, the conditional instruction is restarted. When either the APU

is idle (MC68881) or the APU and CU are idle (MC6888.2) and no exceptions are pending,

FPCP checks for a BSUN exception, evaluates the conditional predicate, and reports the

result to the MPU.

MC68881/MC68882 USER'S MANUAL FREESCALE

6-5

Loading...

Loading...