This primitive is only utilized for the move multiple floating-point data register instruction

when the register list is specified as dynamic. Therefore, when this primitive is issued by

the FPCP (to fetch the register list), CA is always set; DR, PC, and D/A are always clear

(D/A identifies the selected register as a data or address register; zero indicates it is a data

register). The least significant three bits identify the main processor data register that

contains the register list.

Note that the FPCP returns this primitive only once during an instruction dialog. When this

primitive is read from the response CIR, it is discarded by the FPCP, and the response

encoding is changed to the null primitive until the request has been serviced. By doing

this, the FPCP avoids spurious service requests in systems where the MPU is not the main

processor.

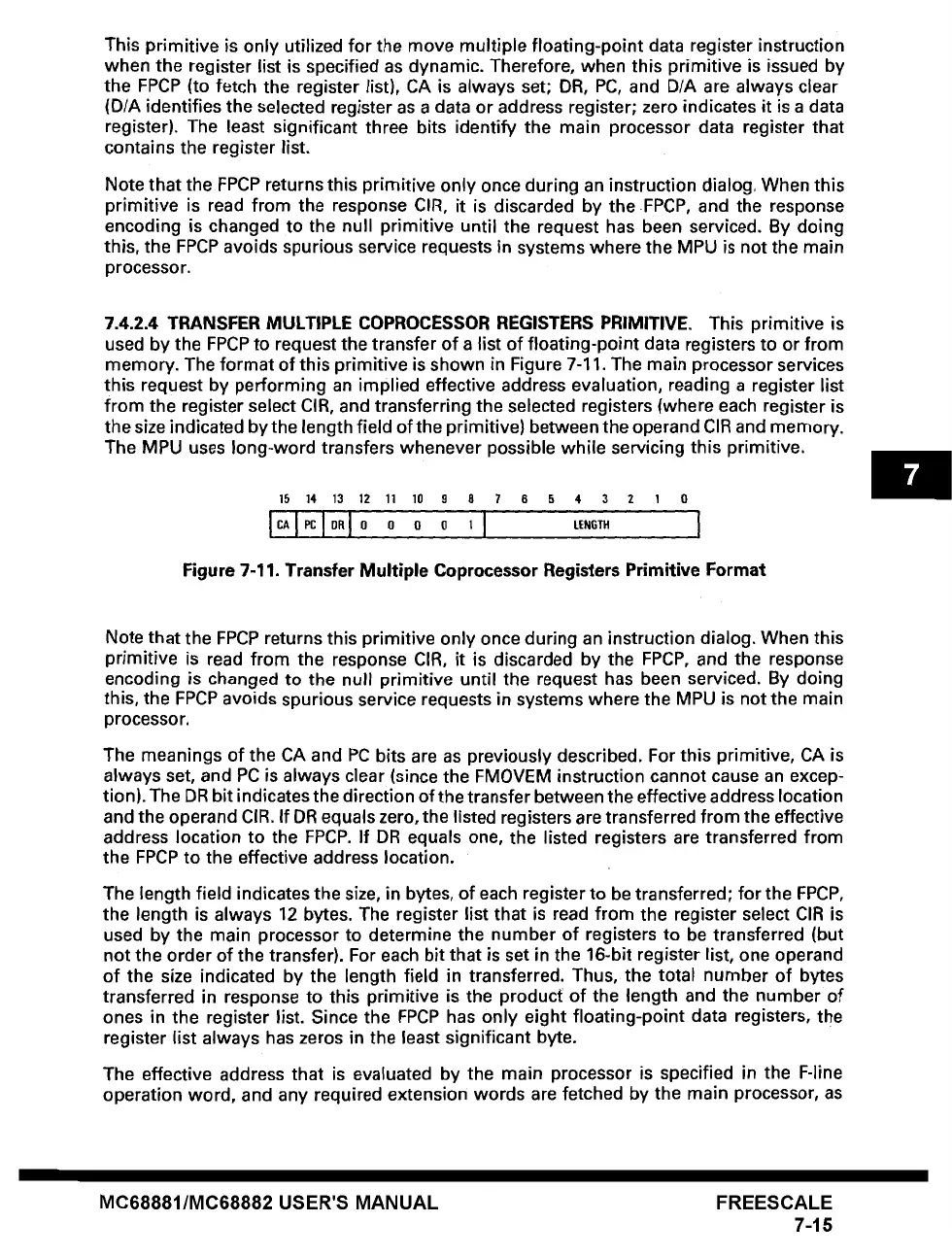

7.4.2.4 TRANSFER MULTIPLE COPROCESSOR REGISTERS PRIMITIVE. This primitive is

used by the FPCP to request the transfer of a list of floating-point data registers to or from

memory. The format of this primitive is shown in Figure 7-11. The main processor services

this request by performing an implied effective address evaluation, reading a register list

from the register select CIR, and transferring the selected registers (where each register is

the size indicated by the length field of the primitive) between the operand CIR and memory.

The MPU uses long-word transfers whenever possible while servicing this primitive.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 O

Figure 7-11. Transfer Multiple Coprocessor Registers Primitive Format

Note that the FPCP returns this primitive only once during an instruction dialog. When this

primitive is read from the response CIR, it is discarded by the FPCP, and the response

encoding is changed to the null primitive until the request has been serviced. By doing

this, the FPCP avoids spurious service requests in systems where the MPU is not the main

processor.

The meanings of the CA and PC bits are as previously described. For this primitive, CA is

always set, and PC is always clear (since the FMOVEM instruction cannot cause an excep-

tion). The DR bit indicates the direction of the transfer between the effective address location

and the operand CIR. If DR equals zero, the listed registers are transferred from the effective

address location to the FPCP. If DR equals one, the listed registers are transferred from

the FPCP to the effective address location.

The length field indicates the size, in bytes, of each register to be transferred; for the FPCP,

the length is always 12 bytes. The register list that is read from the register select CIR is

used by the main processor to determine the number of registers to be transferred (but

not the order of the transfer). For each bit that is set in the 16-bit register list, one operand

of the size indicated by the length field in transferred. Thus, the total number of bytes

transferred in response to this primitive is the product of the length and the number of

ones in the register list. Since the FPCP has only eight floating-point data registers, the

register list always has zeros in the least significant byte.

The effective address that is evaluated by the main processor is specified in the F-line

operation word, and any required extension words are fetched by the main processor, as

MC68881/MC68882 USER'S MANUAL

FREESCALE

7-15

Loading...

Loading...