while both the CU and APU are busy, the appropriate exceptions are enabled, and the

instructions in the CU and APU each report an exception. The MC68882 reports these

exceptions, one at a time, until both exception handlers have been executed. As a con-

sequence, the Conditional instruction is re-started twice to ensure that the reported con-

dition codes contain information reflecting the result of all previous instructions and related

exception handlers. Therefore, a sequential execution model can be guaranteed. It is pos-

sible that a BSUN exception is reported by the conditional instruction, but the BSUN

exception would be reported long after the instructions and related exceptions have been

executed and completed.

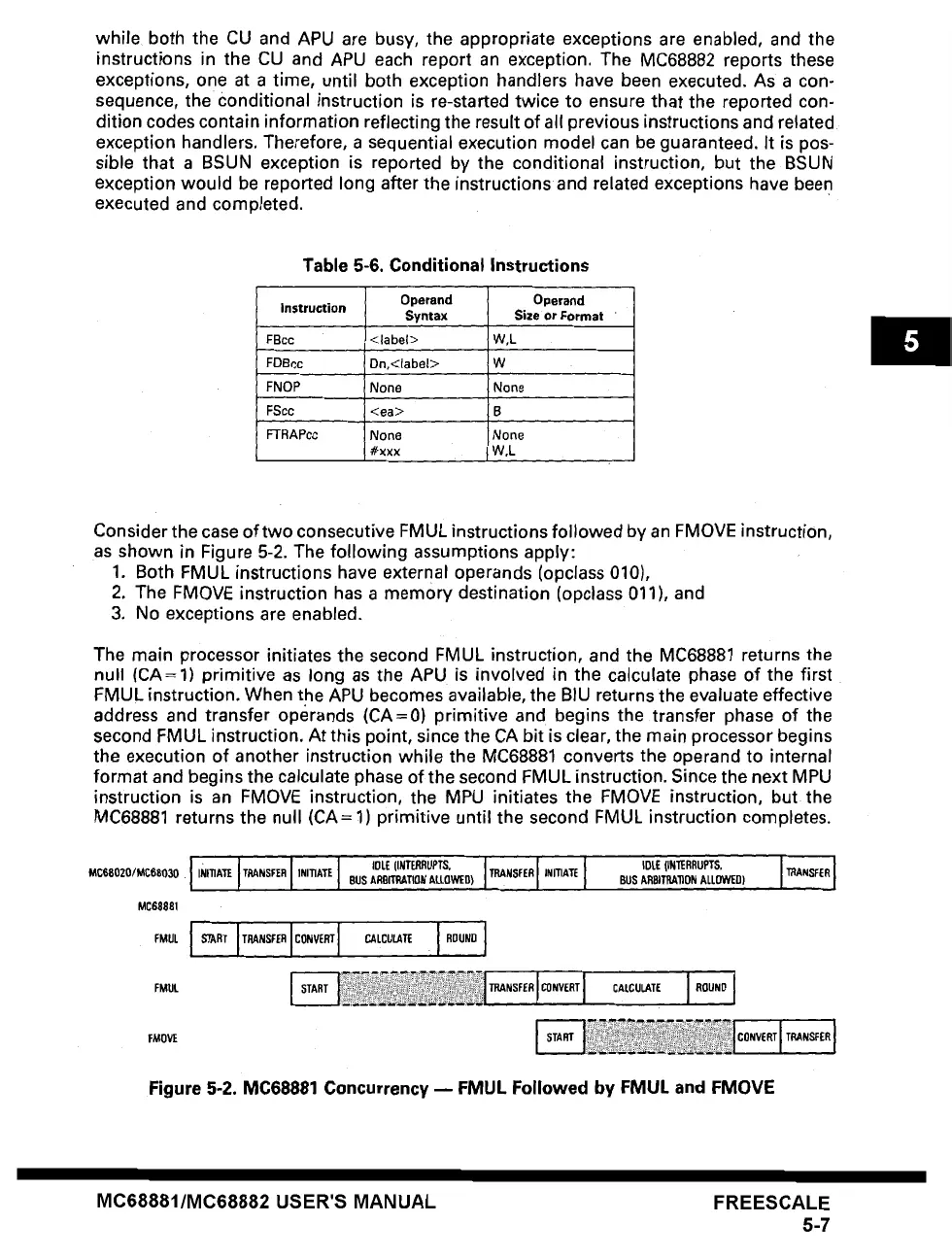

Table 5-6. Conditional Instructions

Instruction Operand Operand

Syntax Size or Format '

FBcc <label> W,L

FDBcc Dn,<label> !W

FNOP None None

FScc <ea> B

FTRAPcc None

#xxx

None

W,L

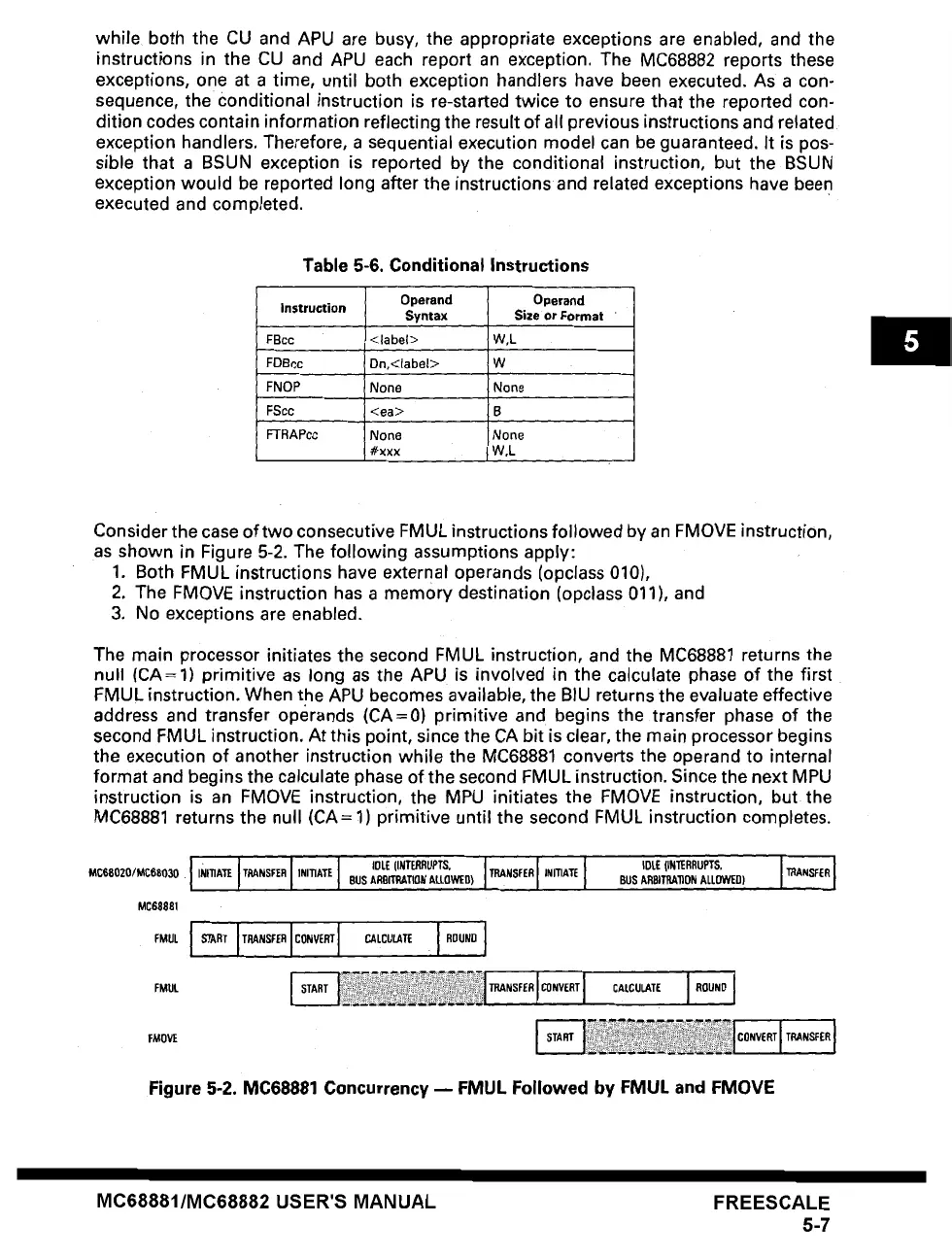

Consider the case of two consecutive FMUL instructions followed by an FMOVE instructiOn,

as shown in Figure 5-2. The following assumptions apply:

1. Both FMUL instructions have external operands (opclass 010),

2. The FMOVE instruction has a memory destination (opclass 011), and

3. No exceptions are enabled.

The main processor initiates the second FMUL instruction, and the MC68881 returns the

null (CA=l) primitive as long as the APU is involved in the calculate phase of the first

FMUL instruction. When the APU becomes available, the BIU returns the evaluate effective

address and transfer operands (CA=0) primitive and begins the transfer phase of the

second FMUL instruction. At this point, since the CA bit is clear, the main processor begins

the execution of another instruction while the MC68881 converts the operand to internal

format and begins the calculate phase of the second FMUL instruction. Since the next MPU

instruction is an FMOVE instruction, the MPU initiates the FMOVE instruction, but the

MC68881 returns the null (CA= 1) primitive until the second FMUL instruction completes.

IMC68881

FMUL

BUS

ARBITRA'110N ALLOWED)

ROUND ,I

FMOVE

Figure 5-2. MC68881 Concurrency -- FMUL Followed by FMUL and FMOVE

MC68881/MC68882 USER'S MANUAL

FREESCALE

5-7

Loading...

Loading...