6

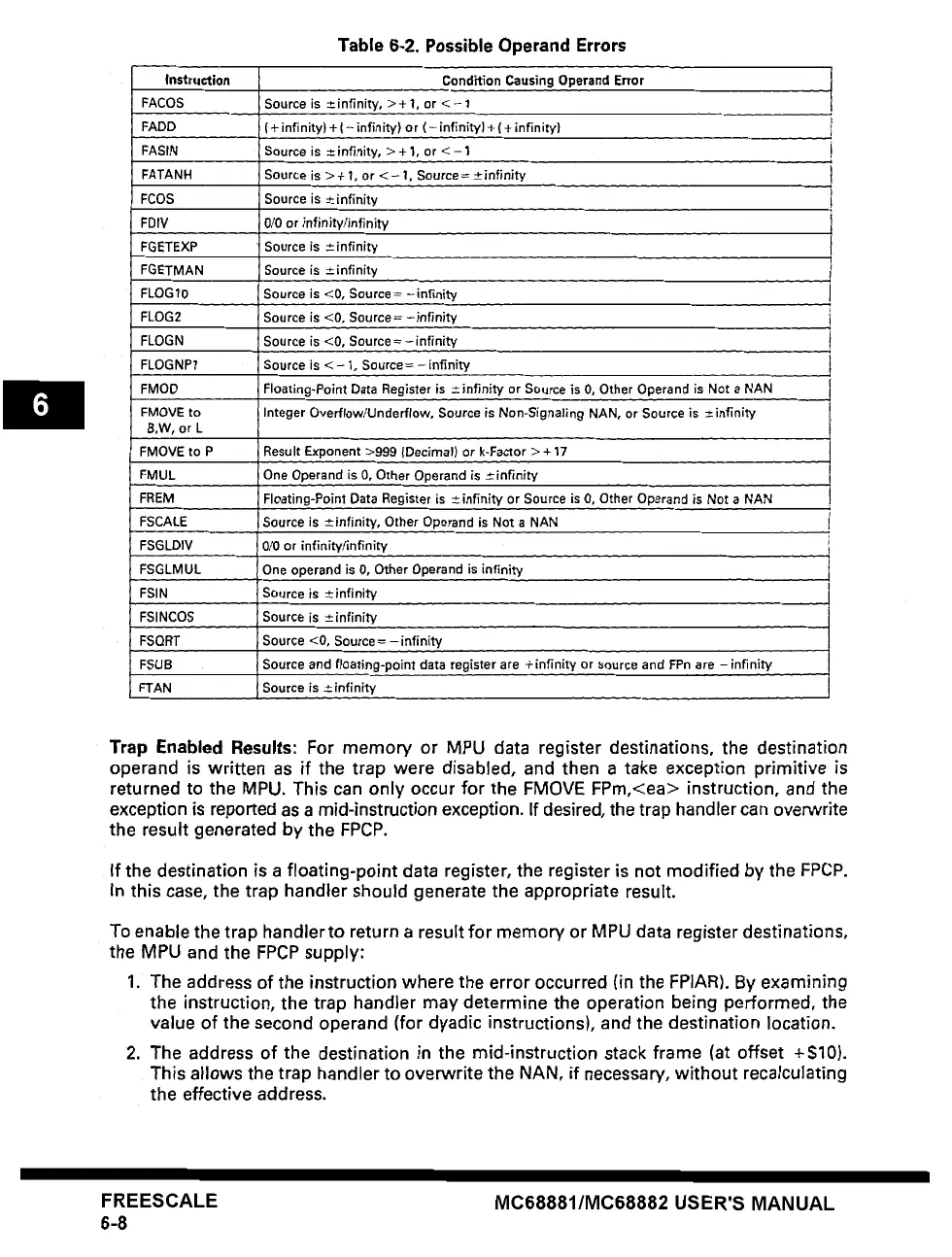

Table 6-2. Possible Operand Errors

Instruction

FACOS

Condition Causing Operand Error

Source is + infinity, > + 1, or < - 1

FADD ( + infinity) + ( - infinity) or ( - infinity) + ( + infinity)

FASIN Source is -+ infinity, > + 1, or <- 1

FATANH Source is > + 1, or < - 1,

Source=

_+infinity

FCOS Source is ±infinity

FDIV

0/0 or infinity/infinity

FGETEXP Source is _+infinity

FGETMAN Source is +-infinity

FLOG1O Source is <0, Source= -infinity

FLOG2 Source is <0, Source=-infinity

FLOGN Source is <0, Source= -infinity

FLOGNP1 Source is <- 1, Source = -infinity

FMOD Floating-Point

Data Register

is _+infinity or Source is 0,

Other Operand

is Not a NAN

FMOVE to Integer Overflow/Underflow, Source is Non-Signaling NAN, or Source is _+infinity

B,W, or L

FMOVE to P Result Exponent >999 (Decimal) or k-Factor > + 17

FMUL One Operand is 0,

Other Operand

is _+infinity

FREM Floating-Point Data Register

is _+infinity or Source is 0,

Other Operand

is Not a NAN

FSCALE Source is _+infinity,

Other Operand

is Not a NAN

FSGLDIV 0/0 or infinity/infinity

FSGLMUL One operand is 0,

Other Operand

is infinity

FSIN Source is _+infinity

FSINCOS Source is _+infinity

FSQRT Source <0, Source=-infinity

FSUB Source and floating-point

data register are

+ infinity or source and FPn are -infinity

FTAN Source is + infinity

Trap Enabled Results: For memory or MPU data register destinations, the destination

operand is written as if the trap were disabled, and then a take exception primitive is

returned to the MPU. This can only occur for the FMOVE FPm,<ea> instruction, and the

exception is reported as a mid-instruction exception. If desired, the trap handler can overwrite

the result generated by the FPCP.

If the destination is a floating-point data register, the register is not modified by the FPCP.

In this case, the trap handler should generate the appropriate result.

To enable the trap handler to return a result for memory or MPU data register destinations,

the MPU and the FPCP supply:

1. The address of the instruction where the error occurred (in the FPIAR). By examining

the instruction, the trap handler may determine the operation being performed, the

value of the second operand (for dyadic instructions), and the destination location.

2. The address of the destination in the mid-instruction stack frame (at offset +$10).

This allows the trap handler to overwrite the NAN, if necessary, without recalculating

the effective address.

FREESCALE

6-8

MC68881/MC68882 USER'S MANUAL

Loading...

Loading...