2

2.2 FLOATING-POINT CONTROL REGISTER

The 32-bit floating-point control register (FPCR) contains an exception enable byte that

enables/disables traps for each class of floating-point exceptions and a mode byte that

sets the user selectable modes.

The control register can be read or written to by the user. Bits 31-16 are reserved for future

definition by

Freescale.

These bits are always read as zero and are ignored during write

operations (but should be zero for future compatibility). This register is cleared by the reset

function or a restore operation of the null state. When cleared, this register provides the

IEEE standard defaults.

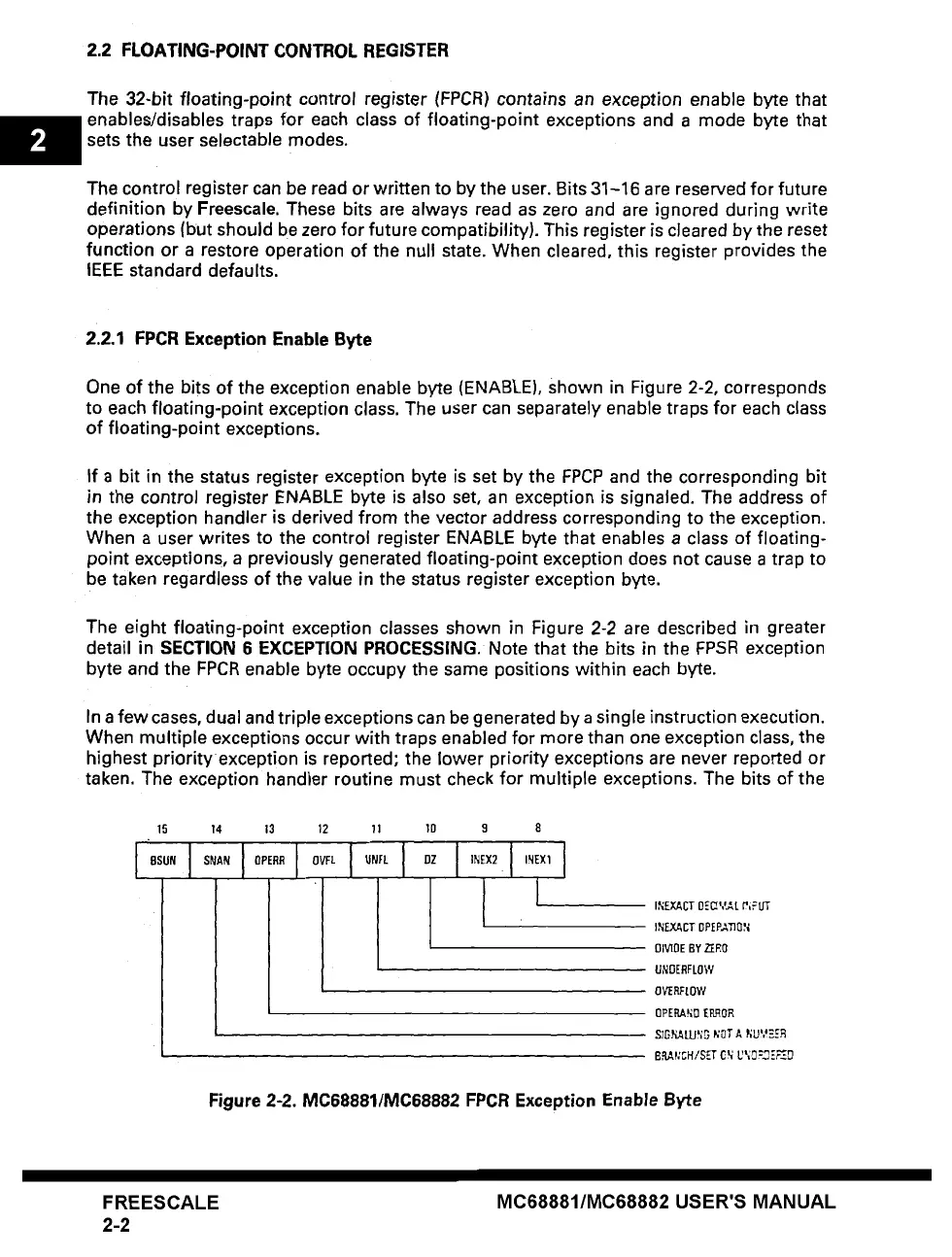

2.2,1 FPCR Exception Enable Byte

One of the bits of the exception enable byte (ENABLE), Shown in Figure 2-2, corresponds

to each floating-point exception class. The user can separately enable traps for each class

of floating-point exceptions.

If a bit in the status register exception byte is set by the FPCP and the corresponding bit

in the control register ENABLE byte is also set, an exception is signaled. The address of

the exception handler is derived from the vector address corresponding to the exception.

When a user writes to the control register ENABLE byte that enables a class of floating-

point exceptions, a previously generated floating-point exception does not cause a trap to

be taken regardless of the value in the status register exception byte.

The eight floating-point exception classes shown in Figure 2-2 are described in greater

detail in SECTION 6 EXCEPTION PROCESSING. Note that the bits in the FPSR exception

byte and the FPCR enable byte occupy the same positions within each byte.

In a few cases, dual and triple exceptions can be generated by a single instruction execution.

When multiple exceptions occur with traps enabled for more than one exception class, the

highest priorityexception is reported; the lower priority exceptions are never reported or

taken. The exception handler routine must check for multiple exceptions. The bits of the

15 14 13 }2 11 ]O 9 8

1

I,~J.ACT 0E~I,~L r';FUT

INEXACT D P[ F.~,T]O '¢

OI~qDE BY ZZF,0

UNDERFLOW

0VERFI.0W

OFERA•D ERROR

Figure 2-2, MC68881/MC68882 FPCR Exception Enable Byte

FREESCALE

2-2

MC68881/MC68882 USER'S MANUAL

Loading...

Loading...