The dr bit set to one indicates a read of the FPCP; dr cleared to zero indicates a write to

the FPCP. The mode field specifies the order of the register transfer and the location of

the register list. The definitions of the mode field bits are (bits shown as X may be either

zero or one):

OX Transfer FP7 through FPO

1X Transfer FPO through FP7

XO Register List is Static

X1 Register List is Dynamic

The order of the register transfer that is selected affects the interpretation of the register

list, because the list is always scanned starting with the most significant bit. Thus, for the

OX encoding of the mode field, the most significant bit of the register list corresponds to

FP7, and the least significant bit corresponds to FPO. For the 1X encoding, this relationship

is reversed.

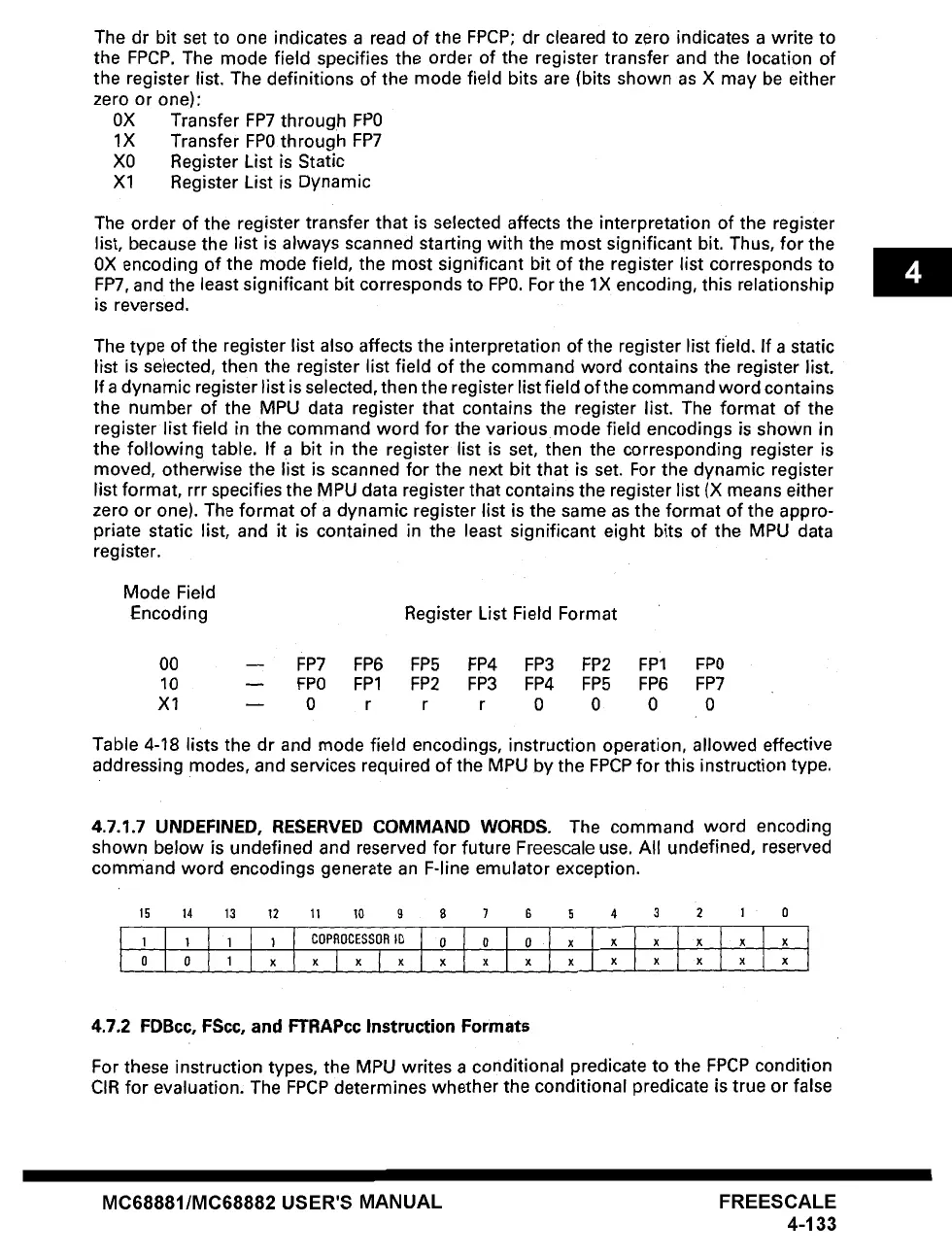

The type of the register list also affects the interpretation of the register list field. If a static

list is selected, then the register list field of the command word contains the register list.

If a dynamic register list is selected, then the register list field of the command word contains

the number of the MPU data register that contains the register list. The format of the

register list field in the command word for the various mode field encodings is shown in

the following table. If a bit in the register list is set, then the corresponding register is

moved, otherwise the list is scanned for the next bit that is set. For the dynamic register

list format, rrr specifies the MPU data register that contains the register list (X means either

zero or one). The format of a dynamic register list is the same as the format of the appro-

priate static list, and it is contained in the least significant eight bits of the MPU data

register.

Mode Field

Encoding

Register List Field Format

O0 m FP7 FP6 FP5 FP4 FP3 FP2 FPi FPO

10 -- FPO FP1 FP2 FP3 FP4 FP5 FP6 FP7

X1 -- 0 r r r 0 0 0 0

Table 4-18 lists the dr and mode field encodings, instruction operation, allowed effective

addressing modes, and services required of the MPU by the FPCP for this instruction type.

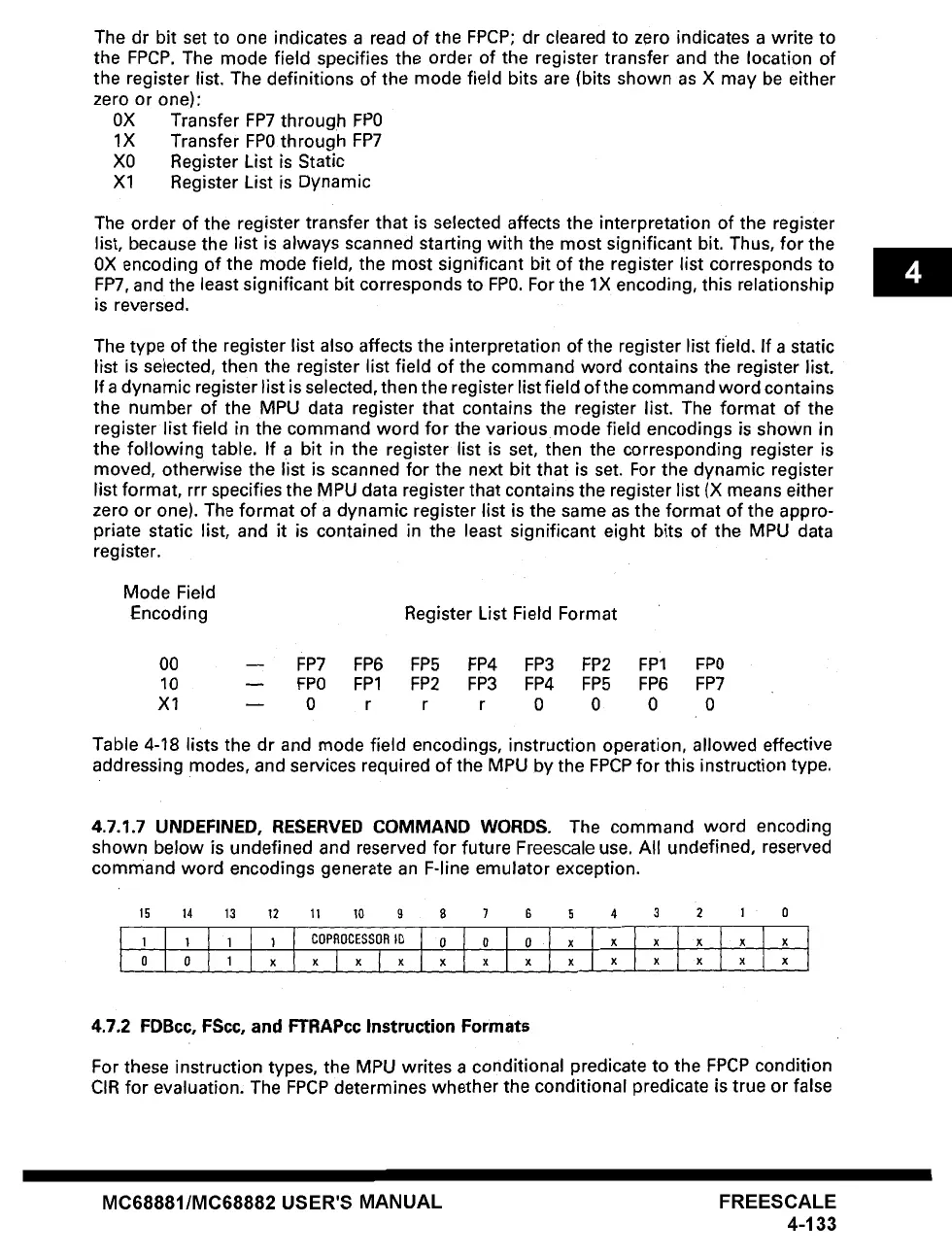

4.7.1.7 UNDEFINED, RESERVED COMMAND WORDS. The command word encoding

shown below is undefined and reserved for future Freescale use. All undefined, reserved

command word encodings generate an F-line emulator exception.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 ! 0

4.7.2 FDBcc, FScc, and FTRAPcc Instruction Formats

For these instruction types, the MPU writes a conditional predicate to the FPCP condition

CIR for evaluation, The FPCP determines whether the conditional predicate is true or false

MC68881/MC68882 USER'S MANUAL

FREESCALE

4-133

Loading...

Loading...