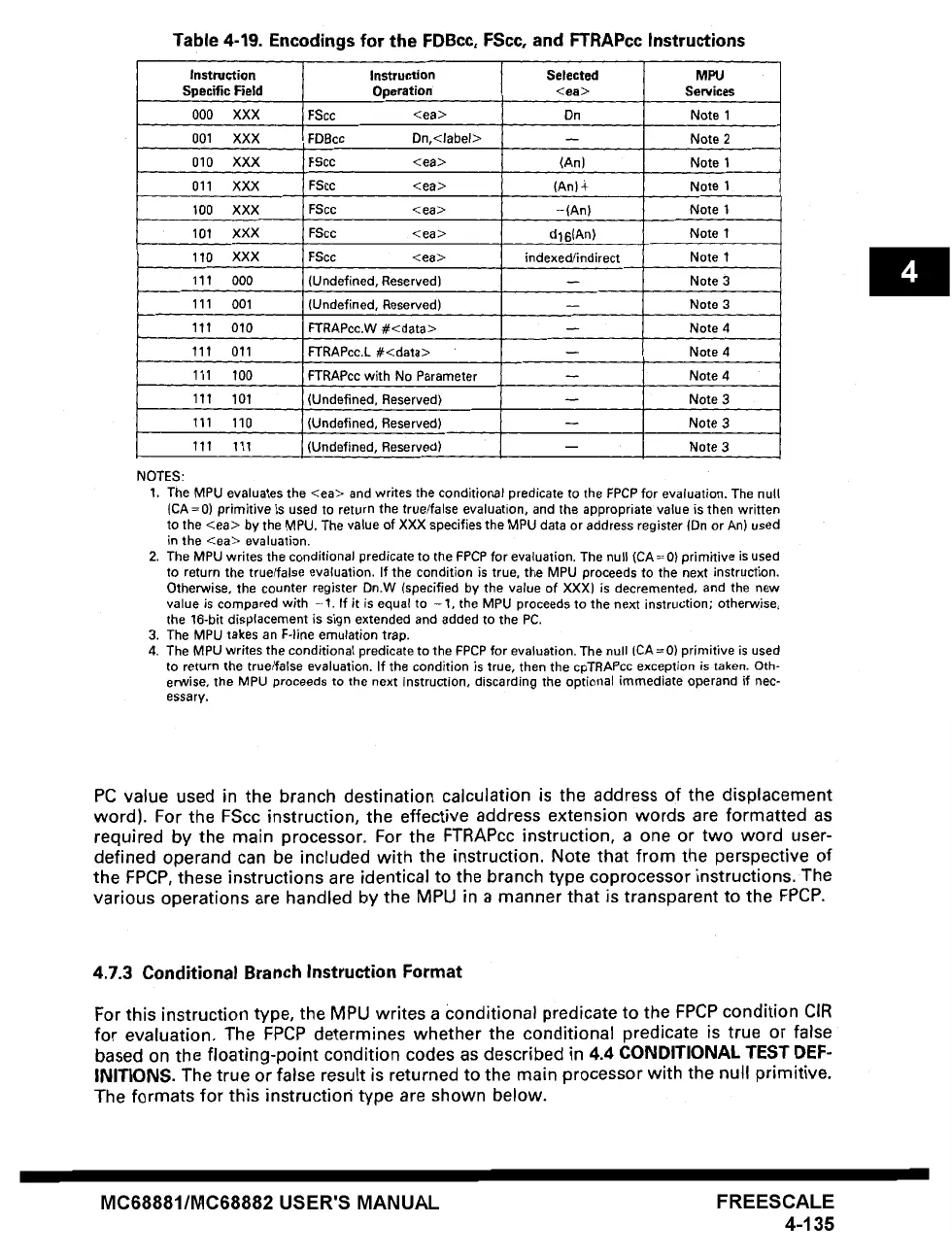

Table 4-19. Encodings for the FDBcc, FScc, and FTRAPcc Instructions

Instruction Instruction Selected MPU

Specific Field Operation <ea> Services

000 XXX FScc

<ea> Dn Note 1

001 XXX , FDBcc Dn,<label> -- Note 2

010 XXX FScc <ea>

011 XXX FScc <ea>

100 XXX FScc <ea>

101 XXX FSec <ea>

110 XXX FScc <ea>

111 000 (Undefined, Reserved)

111 001 (Undefined, Reserved)

111 010 FTRAPcc.W #<data>

(An) Note 1

(An) -~ Note 1

- (An) Note 1

d16{An) Note 1

indexed/indirect Note 1

--

Note 3

--

Note 3

--

Note 4

111 011 FTRAPcc.L #<data> Note 4

111 100 FTRAPcc with No Parameter -- Note 4

111 101 (Undefined, Reserved) -- Note 3

111 110 (Undefined, Reserved) -- Note 3

111 111 (Undefined, Reserved) -- Note 3

NOTES:

1. The MPU

evaluates the <ea> and writes the conditional predicate to the FPCP for evaluation. The null

(CA =0) primitive is used to return the true/false evaluation, and the appropriate value is then written

to the <ea> by the MPU. The value of XXX specifies the MPU data or address register (Dn or An) used

in the <ea> evaluation.

The MPU writes the conditional predicate to the FPCP for evaluation. The null (CA=0) primitive is used

to return the true/false evaluation. If the condition is true, the MPU proceeds to the next instruction.

Otherwise, the counter register Dn.W

(specified

by the value of XXX) is decremented, and the new

value is

compared

with - 1. If it is equal to - 1, the MPU proceeds to the next instruction; otherwise,

the 16-bit disp(acement is sign extended and added to the PC.

The MPU takes an F-line emulation trap.

The MPU writes the conditional predicate to the FPCP for evaluation. The null (CA=0) primitive is used

to return the true/false evaluation. If the condition is true, then the cpTRAPcc exception is taken. Oth*

erwise, the MPU proceeds to the next instruction, discarding the optional immediate operand if nec-

essary.

PC value used in the branch destination calculation is the address of the displacement

word). For the FScc instruction, the effective address extension words are formatted as

required by the main processor. For the FTRAPcc instruction, a one or two word user-

defined operand can be included with the instruction. Note that from the perspective of

the FPCP, these instructions are identical to the branch type coprocessor instructions. The

various operations are handled by the MPU in a manner that is transparent to the FPCP.

4.7.3 Conditional Branch Instruction Format

For this instruction type, the MPU writes a Conditional predicate to the FPCP condition CIR

for evaluation. The FPCP determines whether the conditional predicate is true or false

based on the floating-point condition codes as described in 4.4 CONDITIONAL TEST DEF-

INITIONS. The true or false result is returned to the main processor with the null primitive.

The formats for this instruction type are shown below.

MC68881/MC68882 USER'S MANUAL FREESCALE

4-135

Loading...

Loading...