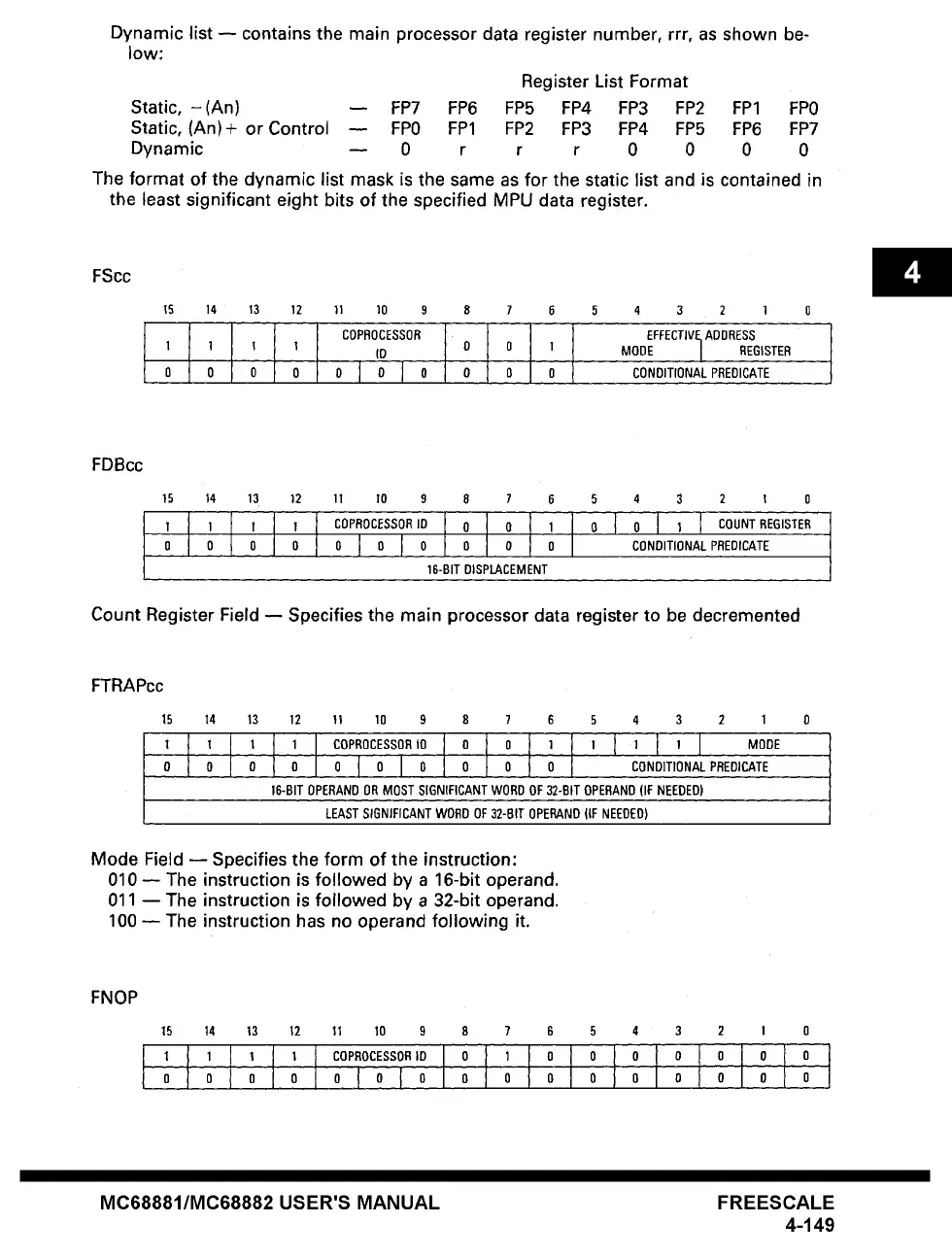

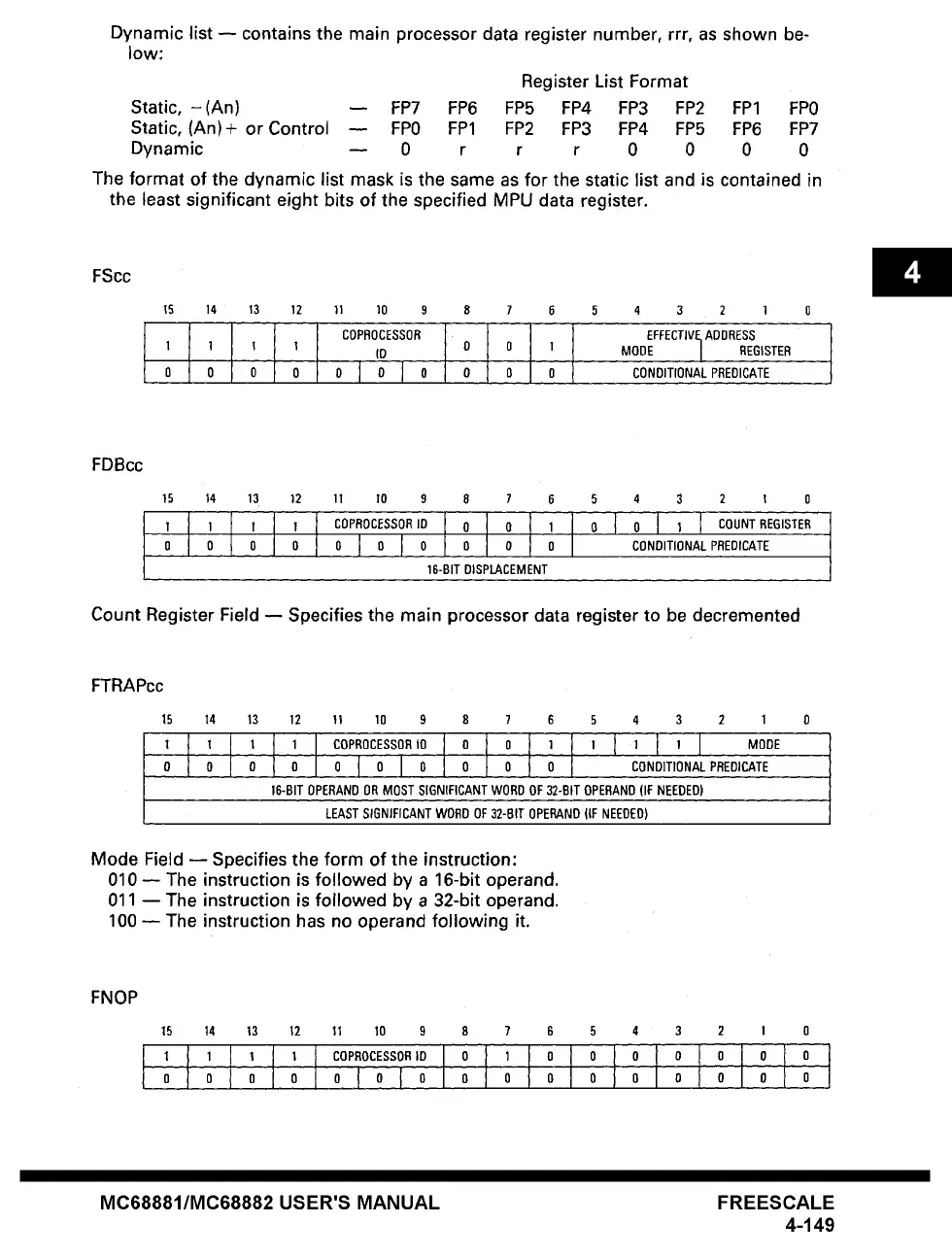

Dynamic list -- contains the main processor data register number, rrr, as shown be-

low:

Register List Format

Static, -(An) -- FP7 FP6 FP5 FP4 FP3 FP2 FP1 FPO

Static, (An)+ or Control -- FPO FP1 FP2 FP3 FP4 FP5 FP6 FP7

Dynamic -- 0 r r r 0 0 0 0

The format of the dynamic list mask is the same as for the static list and is contained in

the least significant eight bits of the specified MPU data register.

FScc

15 14 13 12 11 10 9 8 7 6

COPROCESSOR

1 1 I 1 O 0 1

IO

o o o o o101o

O 0

0

I I

5 4 3 2 1 0

EFFECTIV~ ADDRESS '

MODE | REGISTER

CONDITIONAL PREDICATE

FDBcc

15 14 13 12 11 10 9 8 7 6 5 4 3 2 ~ 0

0 0 0 0 0 l 0 I 0 0 O 0 CONDITIONAL PREDICATE

16-BIT DISPLACEMENT

Count Register Field -- Specifies the main processor data register to be decremented

FTRAPcc

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

I ]

i i i

0 0 0 0 0 ] O I 0 O 0 0 CONDITIONAL PREDICATE

16-GIT 0PERANO OR MOST SIGNIFICA.T WORD OF 3Z-B*T OPERAND (IF NEEDED~

LEAST SIGNIFICANT WORD OF 32-81T OPERAND (IF NEEDED)

Mode Field -- Specifies the form of the instruction:

010 -- The instruction is followed by a 16-bit operand.

011 -- The instruction is followed by a 32-bit operand.

100 -- The instruction has no operand following it.

FNOP

15 14 t3 12 11 10 9 8 7 6 5 4 3 2 I 0

o o , o ololo o o o o o o o o o

MC68881/MC68882 USER'S MANUAL

FREESCALE

4-149

Loading...

Loading...