7

c. There is an FPCP service request (for example, to evaluate the effective address

and transfer data between the effective address and the FPCP). The FPCP may also

request that the MPU query the coprocessor after the service is performed.

d. The MPU is not needed for further processing of the coprocessor instruction. Com-

munication is terminated, and the MPU is free to begin execution of the next

instruction. If the MPU is in the trace mode, the MPU does not take the trace

exception until the FPCP completes the processing of the coprocessor instruction.

Each FPCP instruction type has specific requirements based upon this simplified protocol.

The main processor requests required for each FPCP instruction are described in 4.7

INSTRUCTION ENCODING DETAILS. All FPCP main processor service requests (response

primitives) are described in the following paragraphs. In addition, the dialog used by the

MPU and the FPCP during the execution of each instruction is detailed in 7.5 INSTRUCTION

DIALOGS.

7.4.2 Response Primitives

Data read from the FPCP coprocessor interface response register is referred to as a primitive.

Although the M68000 Family coprocessor interface defines 18 response primitives, the

FPCP only uses six of those primitives. For additional information on the complete set of

response primitives and how they are serviced; refer to the appropriate processor user's

manual. The following paragraphs summarize all FPCP response primitives and how they

are used.

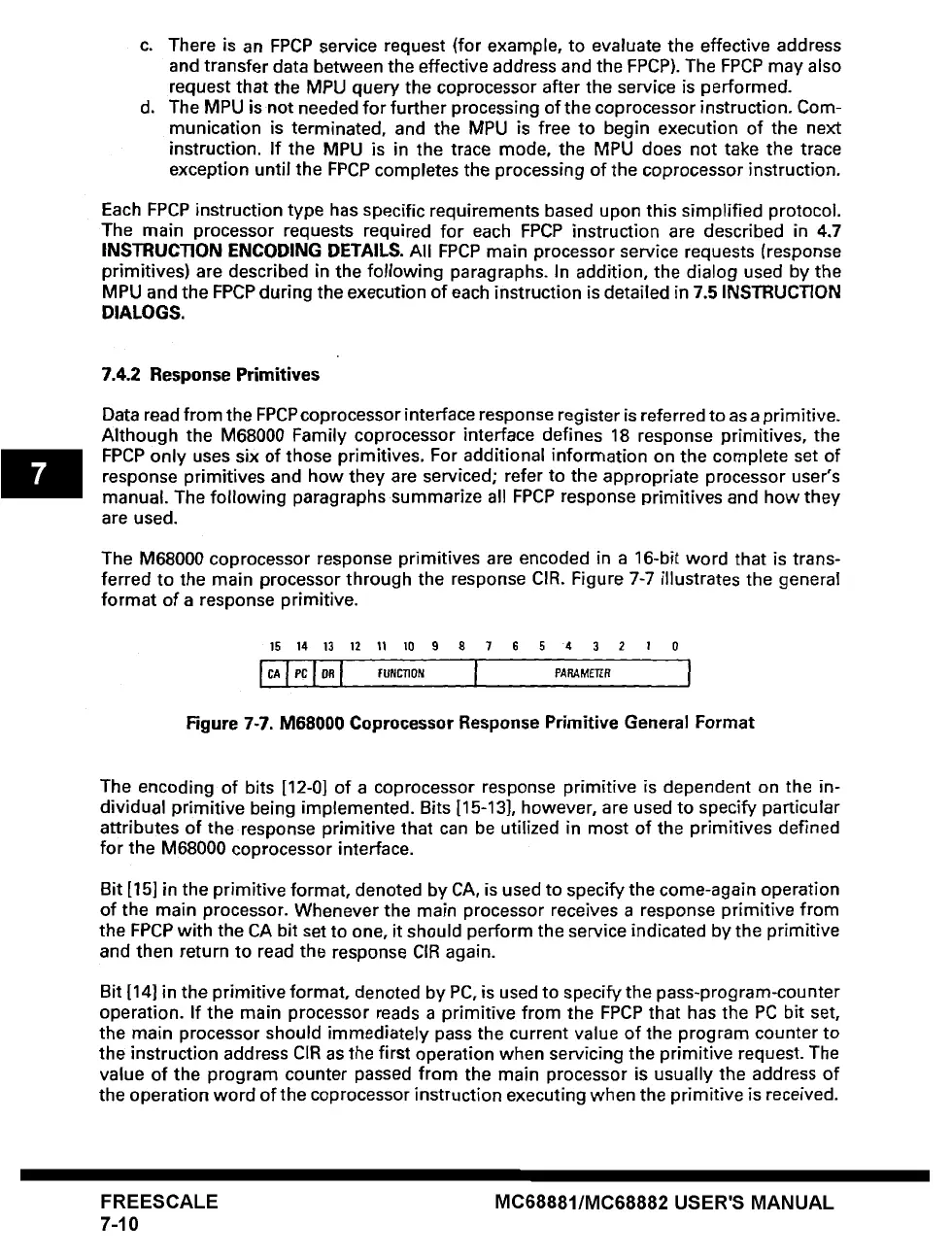

The M68000 coprocessor response primitives are encoded in a 16-bit word that is trans-

ferred to the main processor through the response CIR. Figure 7-7 illustrates the general

format of a response primitive.

15 14 13 12 11 I0 9 8 7 6 5 4 3 2 ! 0

ICAI PCIDR I FUNCTION I PARAMETER I

Figure 7-7. M68000 Coprocessor Response Primitive General Format

The encoding of bits [12-0] of a coprocessor response primitive is dependent on the in-

dividual primitive being implemented. Bits [15-13], however, are used to specify particular

attributes of the response primitive that can be utilized in most of the primitives defined

for the M68000 coprocessor interface.

Bit [15] in the primitive format, denoted by CA, is used to specify the come-again operation

of the main processor. Whenever the main processor receives a response primitive from

the FPCP with the CA bit set to one, it should perform the service indicated by the primitive

and then return to read the response CIR again.

Bit [14] in the primitive format, denoted by PC, is used to specify the pass-program-counter

operation. If the main processor reads a primitive from the FPCP that has the PC bit set,

the main processor should immediately pass the current value of the program counter to

the instruction address CIR as the first operation when servicing the primitive request. The

value of the program counter passed from the main processor is usually the address of

the operation word of the coprocessor instruction executing when the primitive is received.

FREESCALE

7-10

MC68881/MC68882 USER'S MANUAL

Loading...

Loading...