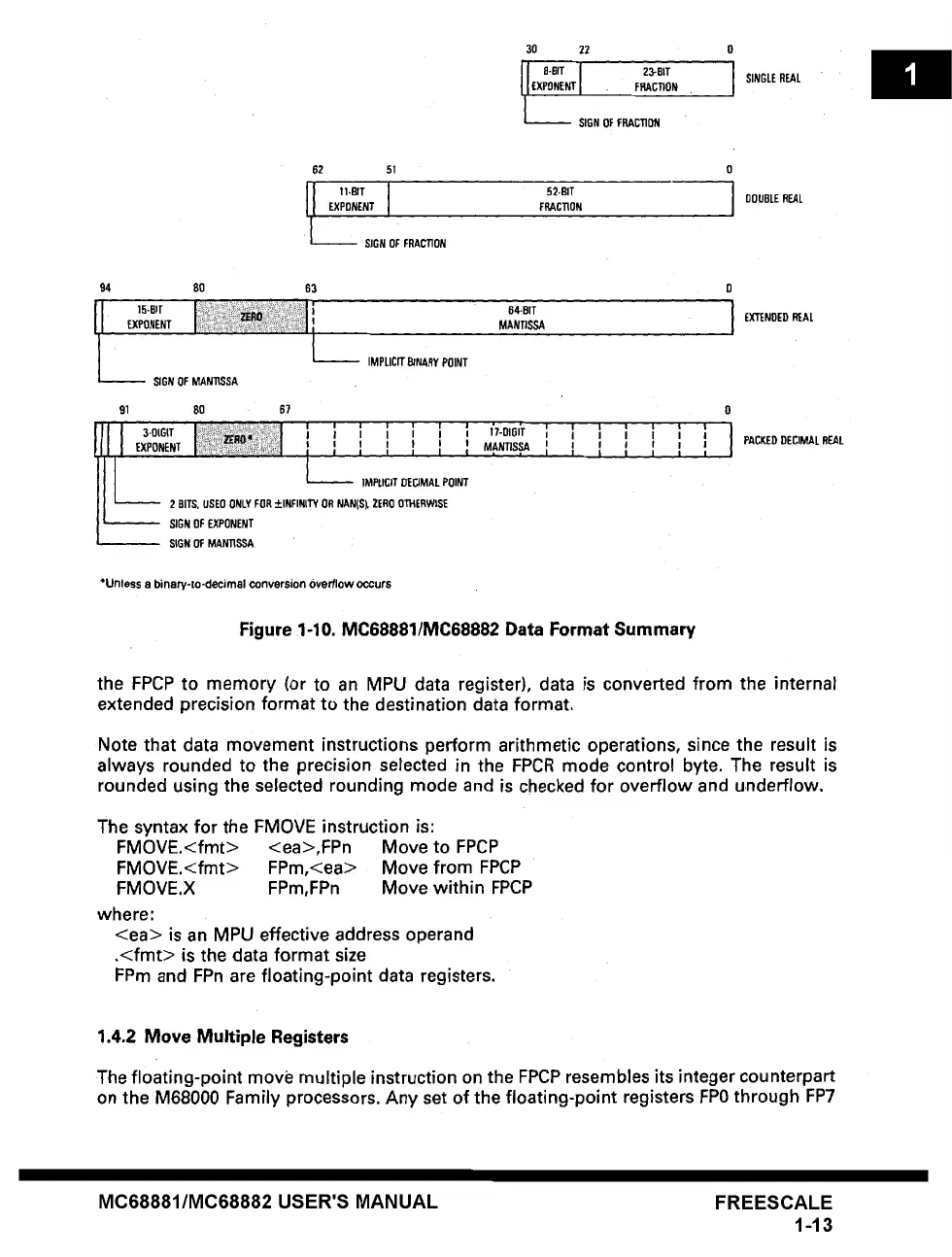

30 22

II -B,T I Z -B,T

J ExP°NENT

I

FRACTION

l-- SIGN OF FRACTION

0

SINGLE REAL

62 51

1 l-BIT

I I EXPONENT I

L___. SIGN 0F FRAC'noN

52-BIT

FRACTION

0

J DOUBLE REAL

94

J

l, 3-O(

EXPOI

II

15-BIT

EXPONENT

SIGN OF MANTISSA

63

64-BIT

MANTISSA

-- IMPLICIT BINARY POINT

O

I EXTENDED REAL

80

67

, ,

l~ IMPLICIT DECIMAL POINT

-- 2 BITS, USEO ONLY FOR +-.INFINII"V OR NAN(S). ZERO OTHERWISE

SIGN OF EXPONENT

SIGN OF MANTISSA

I'7-D,G,~ ', Z i ;

MAN~SSA. . ,' I I :

0

I

i ' :

= I Iz PACKED DECIMAL REAL

*Unless a binary.to-decimal conversion Overflow

occurs

Figure 1-10. MC68881/MC68882 Data Format Summary

the FPCP to memory (or to an MPU data register), data is converted from the internal

extended precision format to the destination data format.

Note that data movement instructions perform arithmetic operations, since the result is

always rounded to the precision selected in the FPCR mode control byte. The result is

rounded using the selected rounding mode and is checked for overflow and underflow.

The syntax for the FMOVE instruction is:

FMOVE.<fmt> <ea>,FPn Move to FPCP

FMOVE.<fmt> FPm,<ea> Move from FPCP

FMOVE.X FPm,FPn Move within FPCP

where:

<ea> is an MPU effective address operand

.<fret> is the data format size

FPm and FPn are floating-point data registers.

1.4.2 Move Multiple Registers

The floating-point move multiple instruction on the FPCP resembles its integer counterpart

on the M68000 Family processors. Any set of the floating-point registers FPO through FP7

MC68881/MC68882 USER'S MANUAL FREESCALE

1-13

Loading...

Loading...