10

FC1

FC0

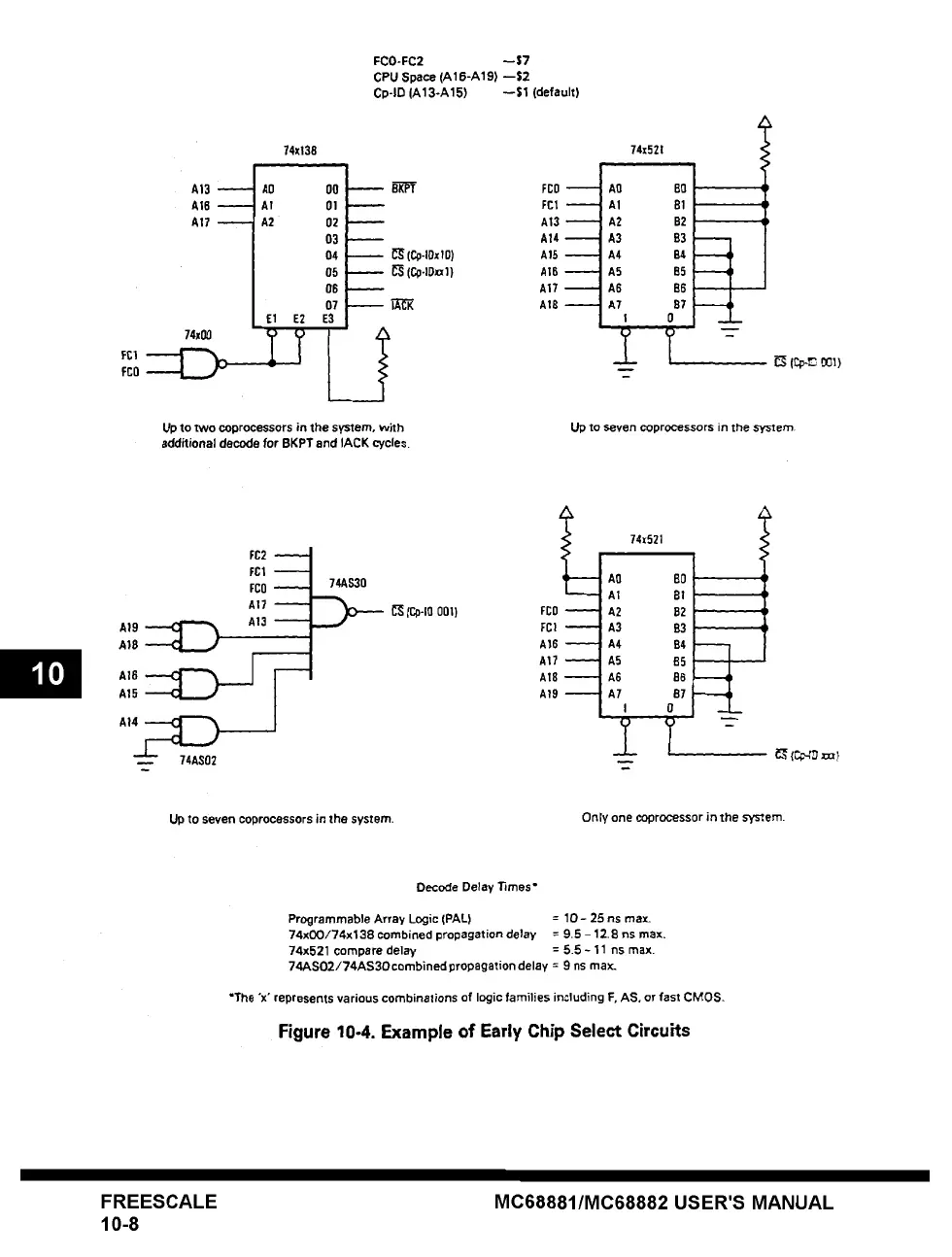

74xl38

A13 - A0

A16 - AT

A17 - A2

E1 E2

74x00

D _T

FCO-FC2 ~$7

CPU Space (A16-A19) --$2

Cp-lD (A13-A15) --$1 (default)

00

01 '-

02

03

04 ,- i~'~ (Cp-IOx l O)

05 i~ (Cp-IDxx 1)

06

07

E3

Up

to two coprocessors in the system, with

additional decode for BKPT and lACK cycles.

FC0

FC1

A13

A14

A15

A16

At7 - -

A18

74x521

A0 80

--

-1 A1 81

A2 B2

A3 B3

A5

A6 86

A7 ! 0B7

±T

i

i

Up to seven coprocessors in the system.

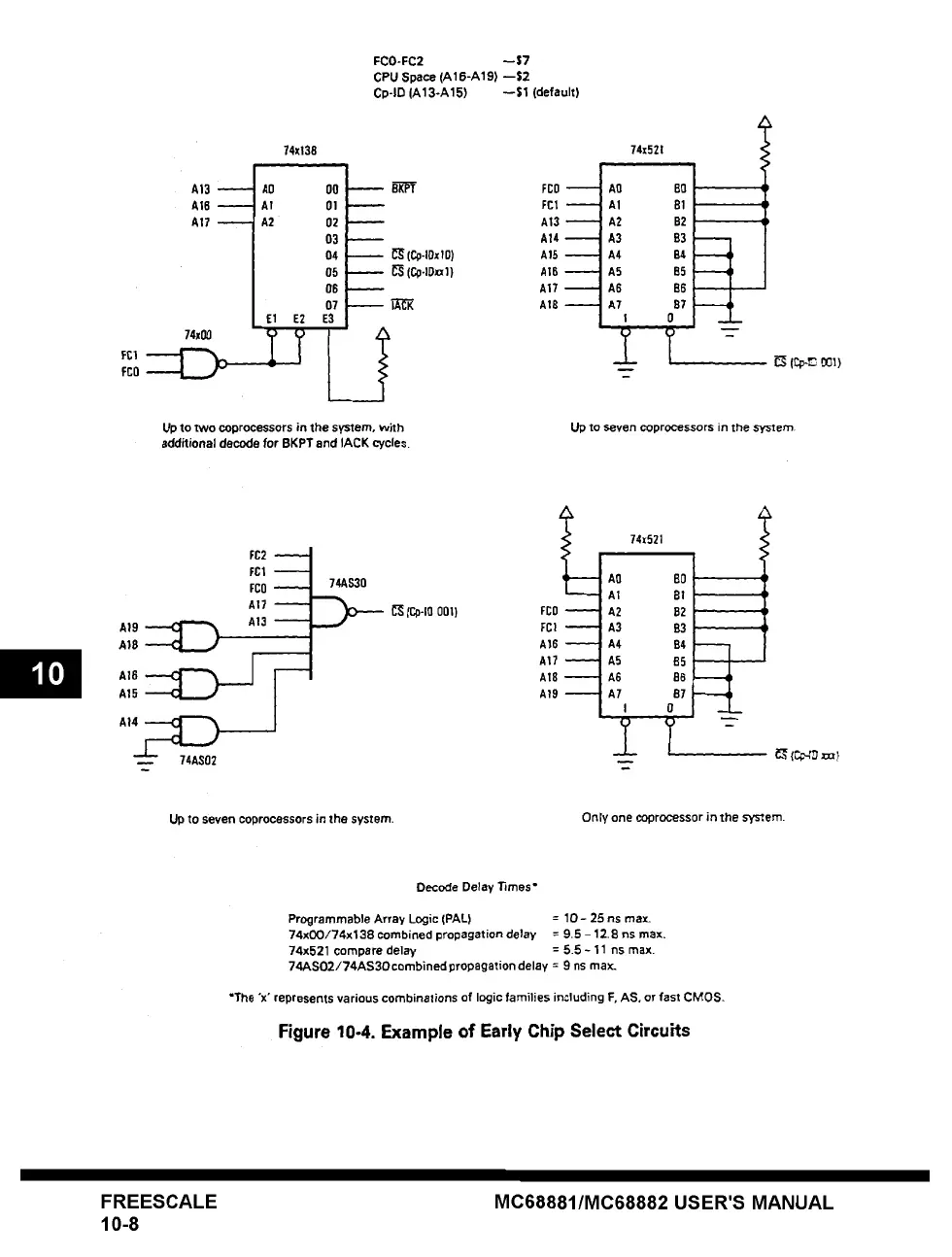

FC1

FC0

A17 ~O

A~B C:Z~J

A15 C[~

J

74AS02

74AS30

, ~ (Cp-IO 001)

,•

74x521

A0

At

FC0 - A2 B2

FC] - A3 B3

A16 - A4 E4

A17 A5 65

A18 -- A6 86

A19 -- A7 B7

I 0

2I

81

Up to seven coprocessors in the system.

Only one coprocessor in the system.

Decode Delay Times"

Programmable Array Logic (PAL) = 10- 25 ns max_

74x00/74x138 combined

propagation delay

= 9.5 - 12.8 ns max.

74x521 compare

delay

= 5.5 - 11 ns max.

74AS02/74AS30cernbinedpropagationdelay = 9 ns max_

*The "x" represents various combinations of logic families including F, AS, or fast CMOS.

Figure 10-4. Example of Early

Chip Select Circuits

FREESCALE

10-8

MC68881/MC68882 USER'S MANUAL

Loading...

Loading...