4

FBcc Branch

Conditionally

FBcc

Operation:

If condition true, then PC + d ~ PC

Assembler

FBcc.<size> <label>

Syntax:

Attributes:

Size = (~/ord, Long)

Description:

If the specified floating-point condition is met, program execution contin-

ues at the location (PC) + displacement. The displacement is a twos-complement

integer that counts the relative distance in bytes. The value of the PC used to calculate

the destination address is the address of the branch instruction plus two. If the dis-

placement size is word, then a 16-bit displacement is stored in the word immediately

following the instruction operation word. If the displacement size is long word, then

a 32-bit displacement is stored in the two words immediately following the instruction

operation word.

The conditional specifier cc selects any one of the 32 floating-point conditional tests

as described in 4.4 CONDITIONAL TEST DEFINITIONS.

Status Register:

Condition Codes: Not affected

Quotient Byte: Not affected

Exception Byte: BSUN

Accrued Exception Byte:

Set if the NAN condition code is set and the

condition selected is an IEEE nonaware test

SNAN Not Affected

OPERR Not Affected

OVFL Not Affected

UNFL Not Affected

DZ Not Affected

INEX2 Not Affected

INEX1 Not Affected

The lOP bit is set if the BSUN bit is set in the exception byte.

No other bit is affected.

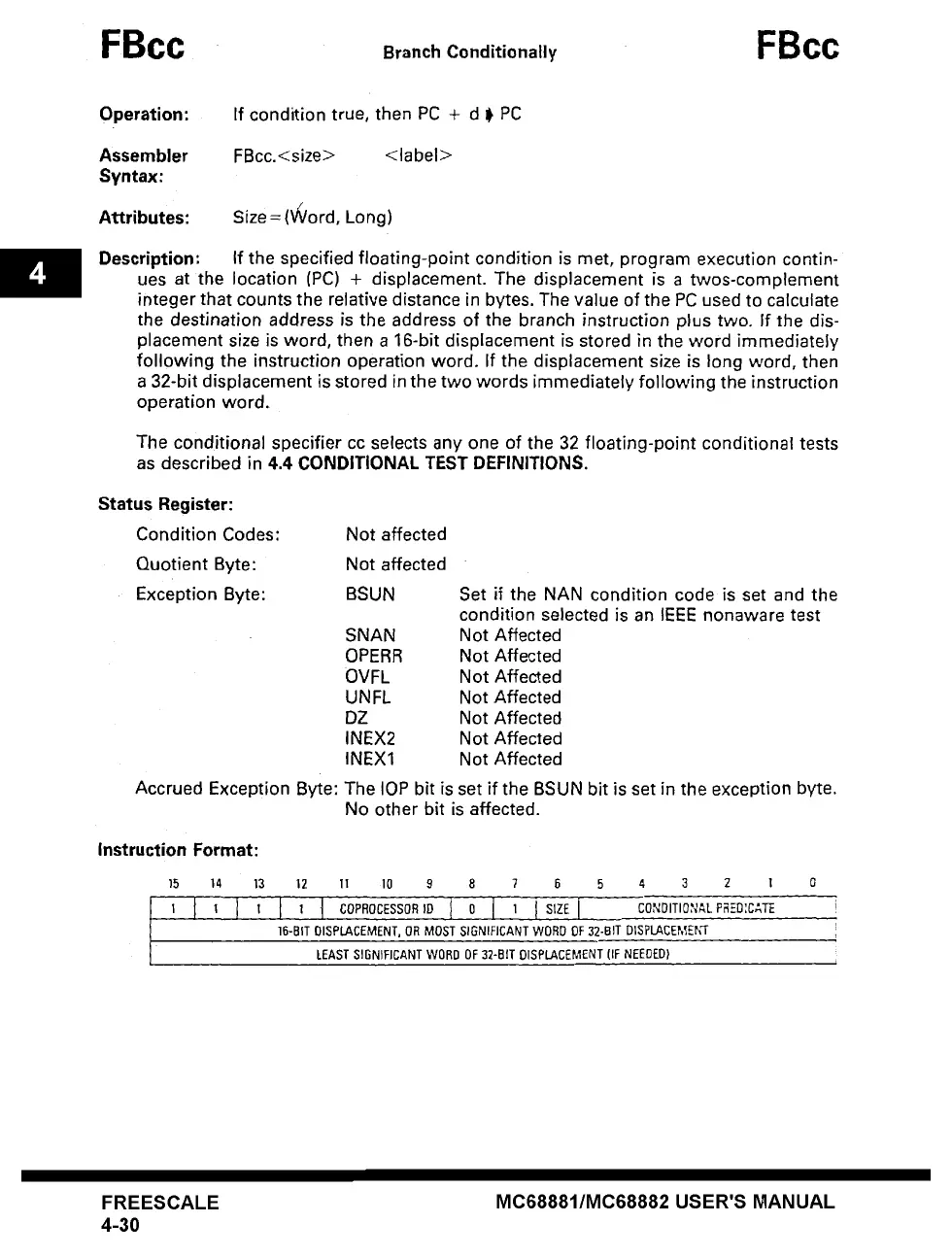

Instruction Format:

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

I ) I I 1 I 1 t COPROCESSORID t 0 I 1 I SiZE I C0~DITI0,'~ALP~ED:CATE .. J

16-BIT 01SPLACEMENT, OR MOST SIGNIFICANT WORD OF 32-BIT DISPLAC:EMEhq"

LEAST SIGNIFICANT WORD OF 32-BIT DISPLACEMENT (IF NEEDED)

FREESCALE

4-30

MC68881/MC68882 USER'S MANUAL

Loading...

Loading...