4

FTENTOX

10X

FTENTOX

Instruction Fields:

Coprocessor ID Field -- Specifies which coprocessor in the system is to execute this

instruction. Freescale assemblers default to ID = 1 for the FPCP.

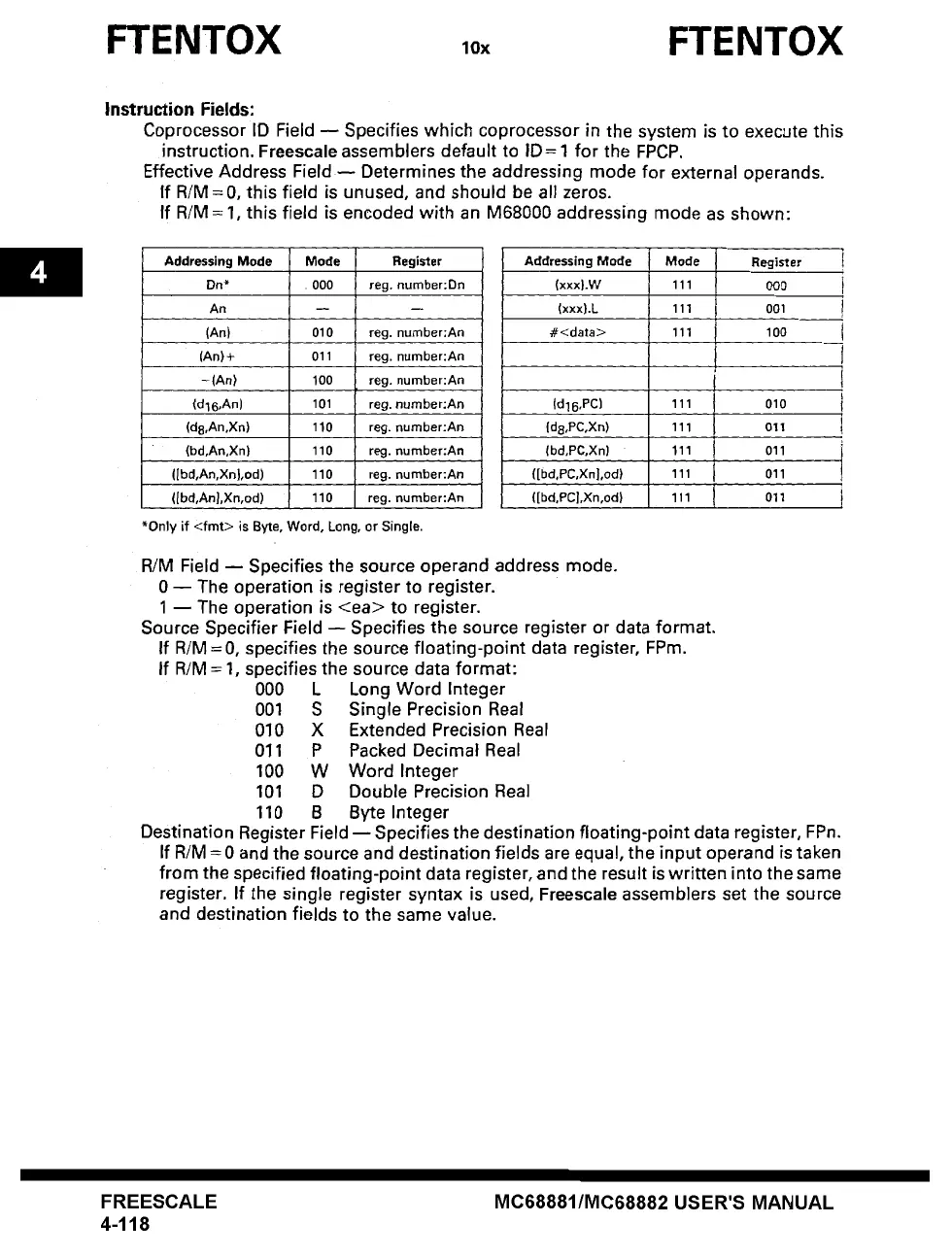

Effective Address Field -- Determines the addressing mode for external operands.

If R/M =0, this field is unused, and should be all zeros.

If R/M = 1, this field is encoded with an M68000 addressing mode as shown:

Addressing Mode Mode

Dn* .000

An

(An) 010

(An) + 011

-(An) 100

(d16,An) 101

(d8,An,Xn) 110

(bd,An,Xn) 110

([bd,An,XnJ,od) 110

([bd,AnJ,Xn,od) : 110

Register

reg. number:Dn

reg. number:An

reg. number:An

reg. number:An

reg. number:An

reg. number:An

reg. number:An

reg. number:An

reg. number:An

*Only if <fmt> is Byte, Word, Long, or Single.

Addressing Mode

(xxxl.W

(xxx}.L

#<data>

(d16,PC)

{ds,PC,Xn)

(bd,PC,Xn}

{[bd,PC,Xn],od)

([bd,PC],Xn,od)

Mode

111

111

111

111

111

111

l

111

111

1

Register

000

001

100

010

011

011

011

011

R/M Field m Specifies the source operand address mode.

0 m The operation is register to register.

1 ~ The operation is <ea> to register.

Source Specifier Field ~ Specifies the source register or data format.

If R/M =0, specifies the source floating-point data register, FPm.

If R/M = 1, specifies the source data format:

000 L Long Word Integer

001 S Single Precision Real

010 X Extended Precision Real

011 P Packed Decimal Real

100 W Word Integer

101 D Double Precision Real

110 B Byte Integer

Destination Register Field ~ Specifies the destination floating-point data register, FPn.

If R/M = 0 and the source and destination fields are equal, the input operand is taken

from the specified floating-point data register, and the result is written into the same

register. If the single register syntax is used, Freescale assemblers set the source

and destination fields to the same value.

FREESCALE

4-118

MC68881/MC68882 USER'S MANUAL

Loading...

Loading...