FTST

Test Operand

FTST

Operation:

Assembler

Syntax:

Attributes:

Description:

Condition Codes for Operand 0 FPCC

FTST.<fmt> <ea>

FTST,X FPm

Format = (Byte, Word, Long, Single, Double, Extended, Packed)

Converts the source operand to extended precision (if necessary) and sets

the condition code bits according to the data type of the result.

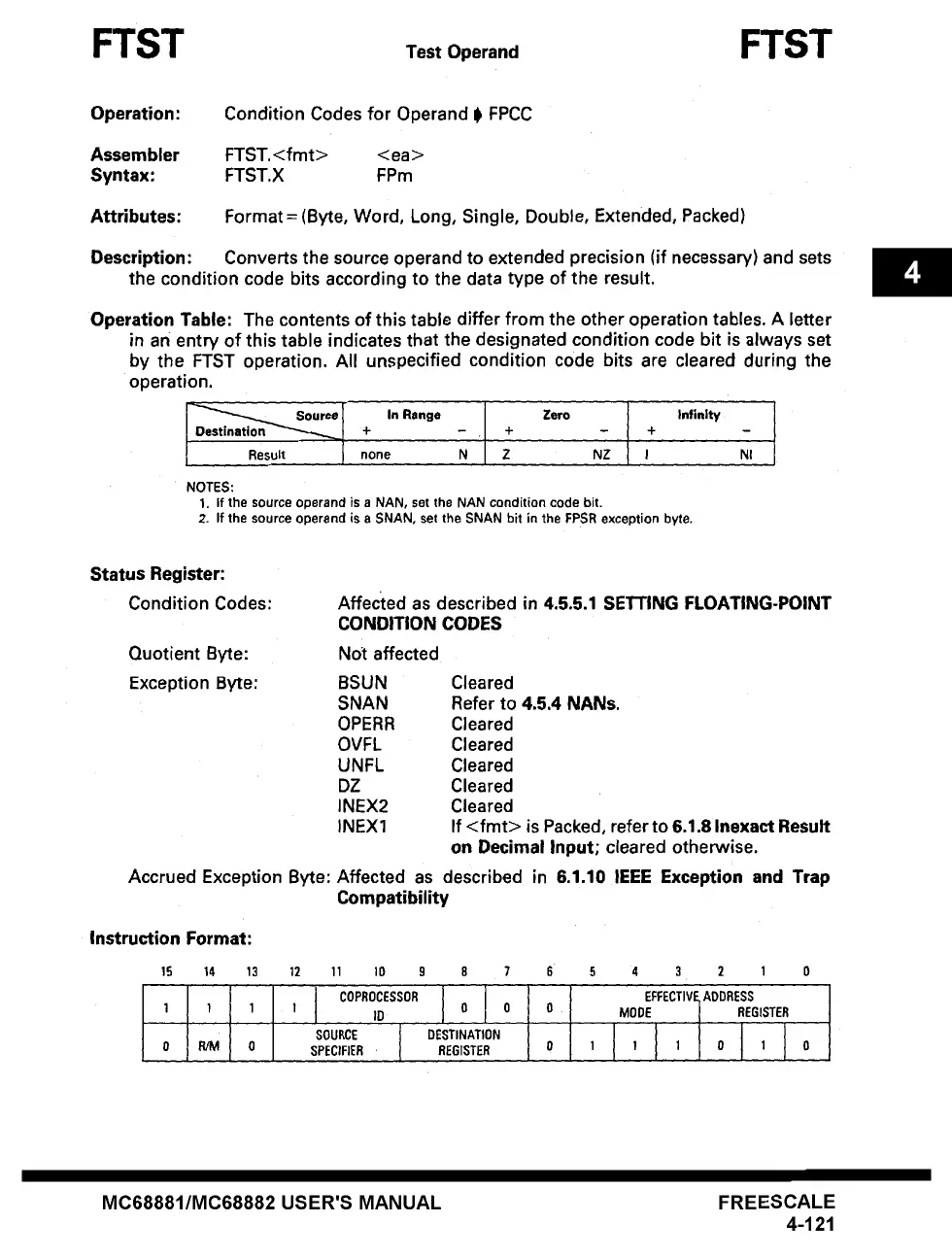

Operation Table:

The contents of this table differ from the other operation tables. A letter

in an entry of this table indicates that the designated condition code bit is always set

by the FTST operation. All unspecified condition code bits are cleared during the

operation.

Source In

Range

Destination

~ +

Result none N

Zero

Infinity

-I- - -I- -

Z NZ I NI

NOTES:

1. if the source operand is a NAN,

set the

NAN condition code bit.

2. If the source operand is a SNAN, set the SNAN bit in the FPSR exception byte.

Status Register:

Condition Codes:

Quotient Byte:

Exception Byte:

Accrued Exception Byte:

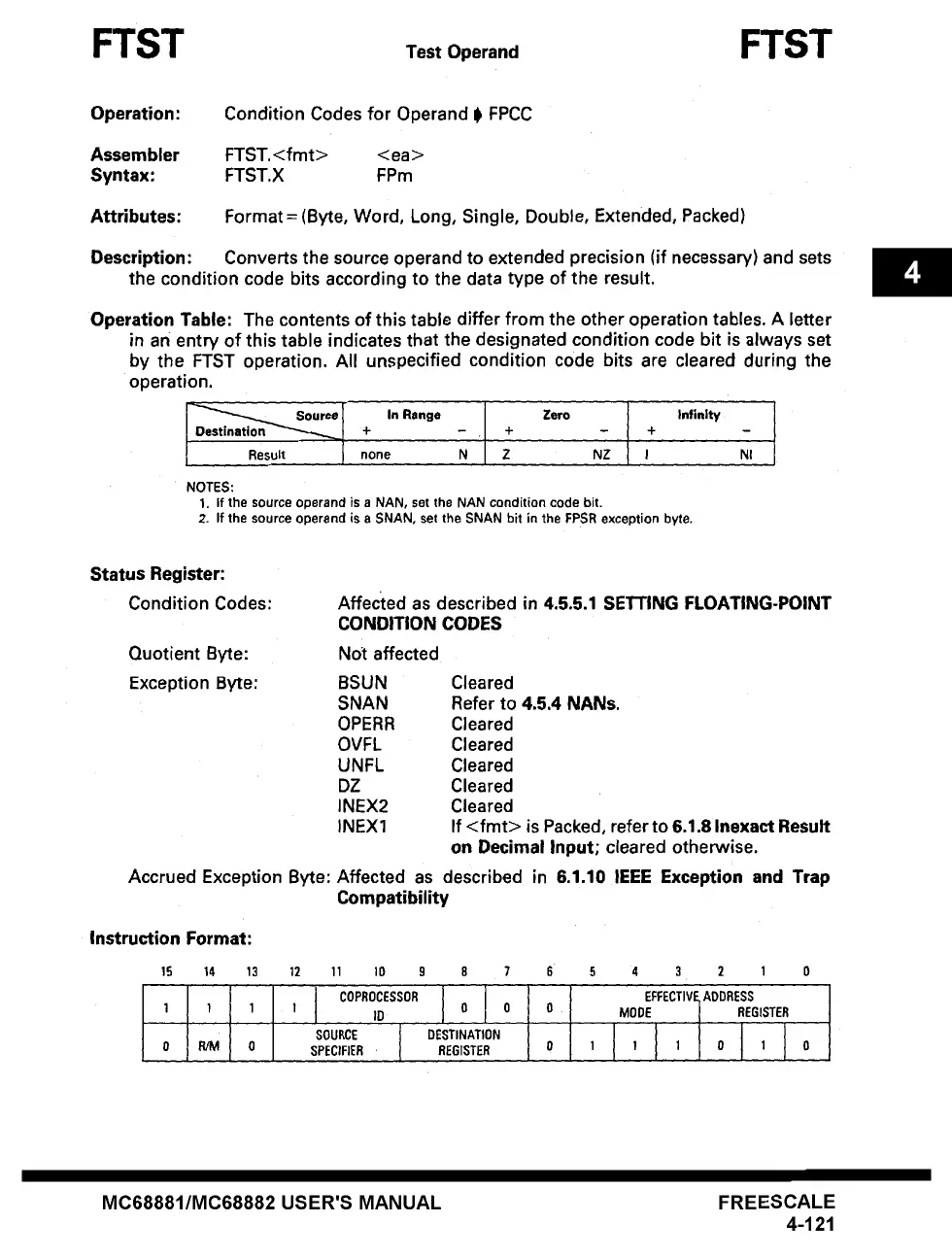

Instruction Format:

15 14 13

1 1 1

0 R/M 0

Affected as described in 4.5.5.1 SETTING FLOATING-POINT

CONDITION

CODES

Not affected

BSUN

SNAN

OPERR

OVFL

UNFL

DZ

INEX2

INEX1

Cleared

Refer to 4.5.4

NANs.

Cleared

Cleared

Cleared

Cleared

Cleared

If <fret> is Packed, refer to 6.1.8 Inexact Result

on Decimal Input;

cleared otherwise.

Affected as described in 6.1.10 IEEE

Exception and Trap

Compatibility

12 11 10 9 8 7 6 5 4 3 2 1 0

I COPROCESSOR EFFECTIV~ ADDRESS

1 ID 0 0 0 MODE | REGISTER

SPECIFIER REGISTER 0 1 1 1 0 1 0

MC68881/MC68882 USER'S MANUAL FREESCALE

4-121

Loading...

Loading...