6

exponent. Therefore, these instructions can never report an underflow as long as

the intermediate result is large enough to be represented in the extended precision

format.

Trap Disabled

Results: The result that is stored in the destination is either a denormalized

number or zero. The intermediate result is always normalized because the FPCP ALU and

temporary registers use a 17-bit exponent. Denormalization is accomplished by shifting

the mantissa of the intermediate result to the right while incrementing the exponent until

it is equal to the denormalized exponent value for the destination format. The denormalized

intermediate result is rounded to the selected rounding precision or destination format.

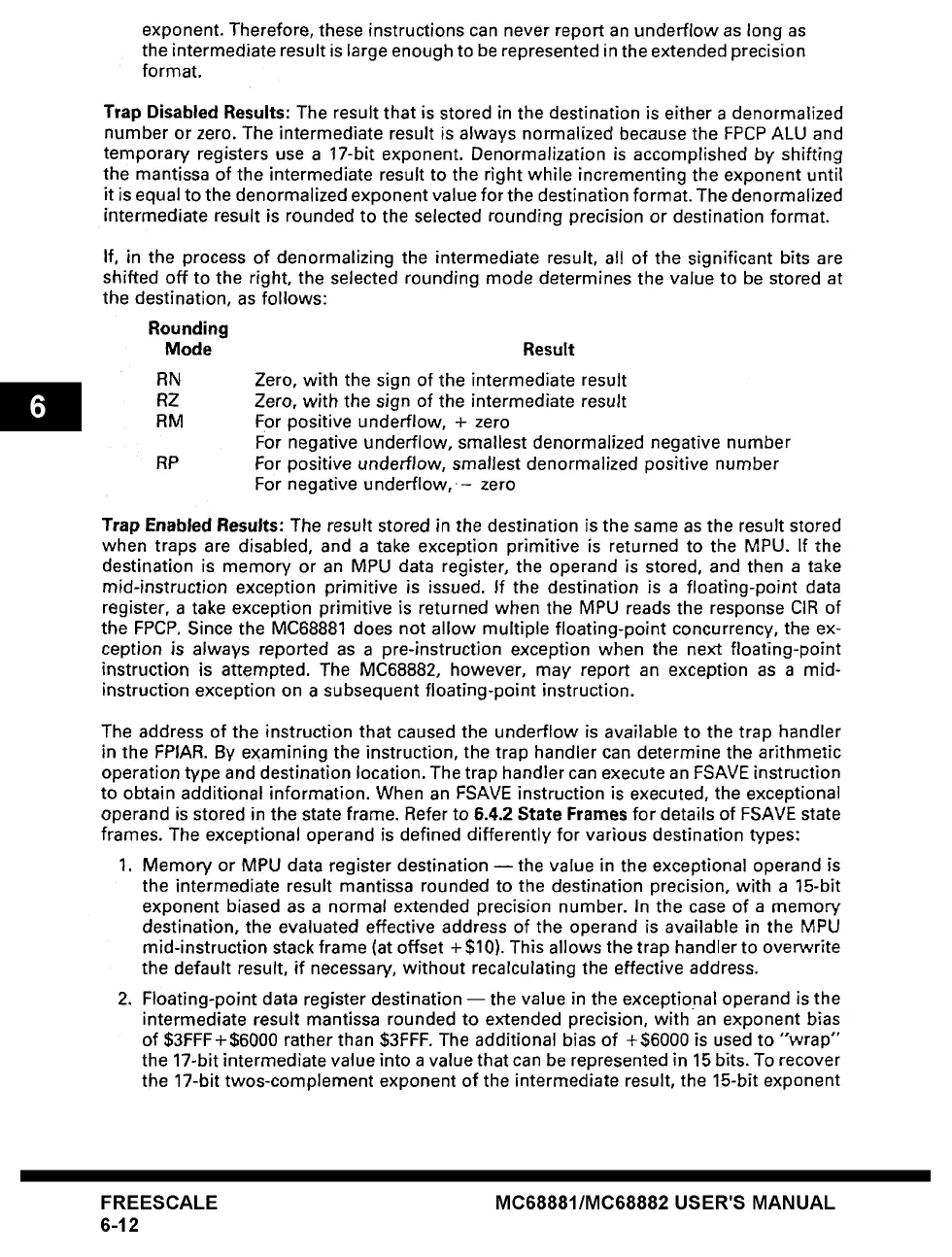

If, in the process of denormalizing the intermediate result, all of the significant bits are

shifted off to the right, the selected rounding mode determines the value to be stored at

the destination, as follows:

Rounding

Mode

RN

RZ

RM

RP

Result

Zero, with the sign of the intermediate result

Zero, with the sign of the intermediate result

For positive underflow, + zero

For negative underflow, smallest denormalized negative number

For positive

underflow, smallest denormalized positive number

For negative underflow, - zero

Trap Enabled Results:

The result stored in the destination is the same as the result stored

when traps are disabled, and a take exception primitive is returned to the MPU. If the

destination is memory or an MPU data register, the operand is stored, and then a take

mid-instruction exception primitive is issued. If the destination is a floating-point data

register, a take exception primitive is returned when the MPU reads the response CIR of

the FPCP. Since the MC68881 does not allow multiple floating-point concurrency, the ex-

ception is always reported as a pre-instruction exception when the next floating-point

instruction is attempted. The MC68882, however, may report an exception as a mid-

instruction exception on a subsequent floating-point instruction.

The address of the instruction that caused the underflow is available to the trap handler

in the FPIAR. By examining the instruction, the trap handler can determine the arithmetic

operation type and destination location. The trap handler can execute an FSAVE instruction

to obtain additional information. When an FSAVE instruction is executed, the exceptional

operand is stored in the state frame. Refer to 6.4.2

State Frames

for details of FSAVE state

frames. The exceptional operand is defined differently for various destination types:

1. Memory or MPU data register destination -- the value in the exceptional operand is

the intermediate result mantissa rounded to the destination precision, with a 15-bit

exponent biased as a normal extended precision number. In the

case of a memory

destination, the evaluated effective address of the operand is available in the MPU

mid-instruction stack frame (at offset + $10). This allows the trap handler to overwrite

the default result, if necessary, without reca/culating the effective address.

2. Floating-point data register destination -- the value in the exceptional operand is the

intermediate result mantissa rounded to extended precision, with an exponent bias

of $3FFF+$6000 rather than $3FFF. The additional bias of +$6000 is used to "wrap"

the 17-bit intermediate value into a value that can be represented in 15 bits. To recover

the 17-bit twos-complement exponent of the intermediate result, the 15-bit exponent

FREESCALE

6-12

MC68881/MC68882 USER'S MANUAL

Loading...

Loading...