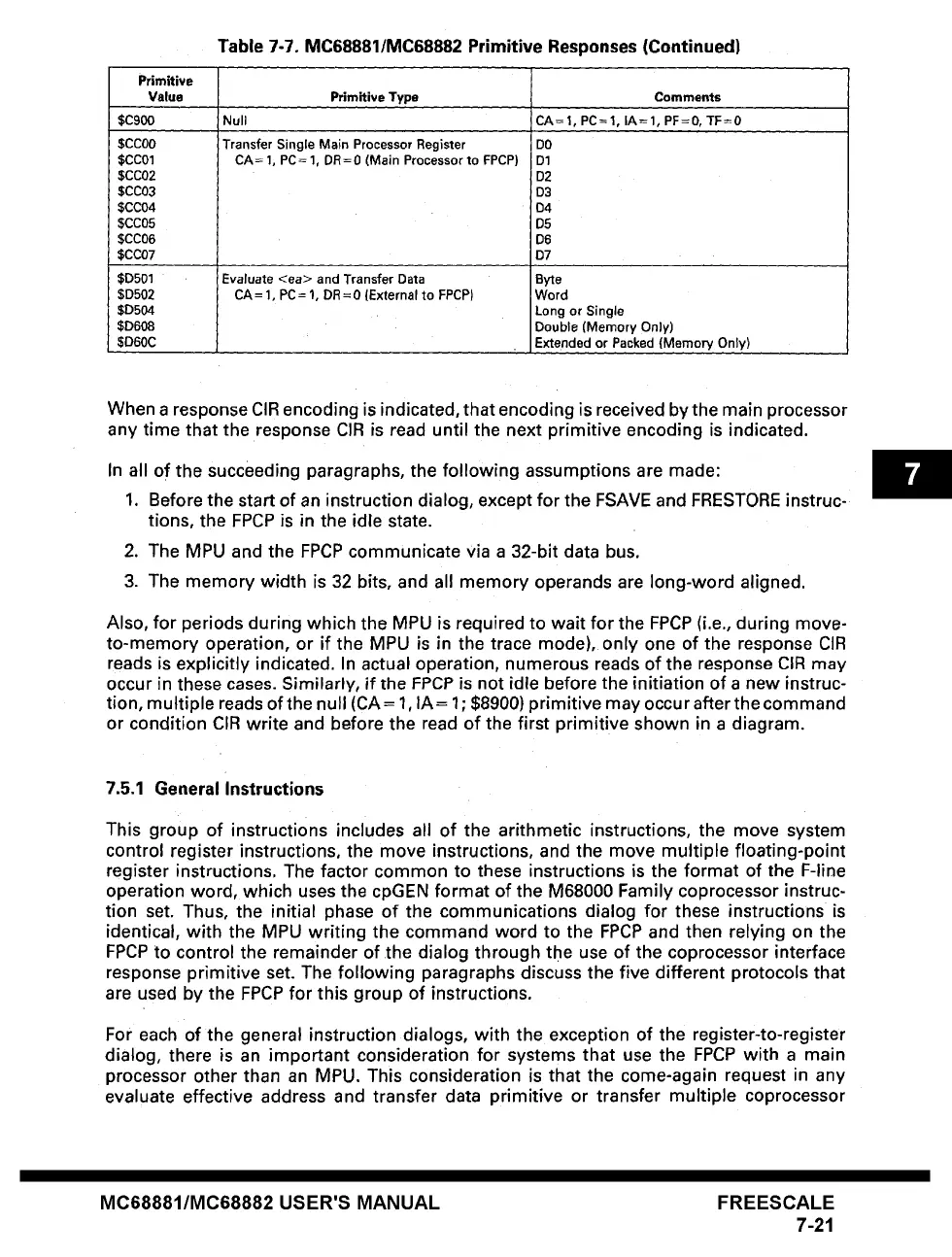

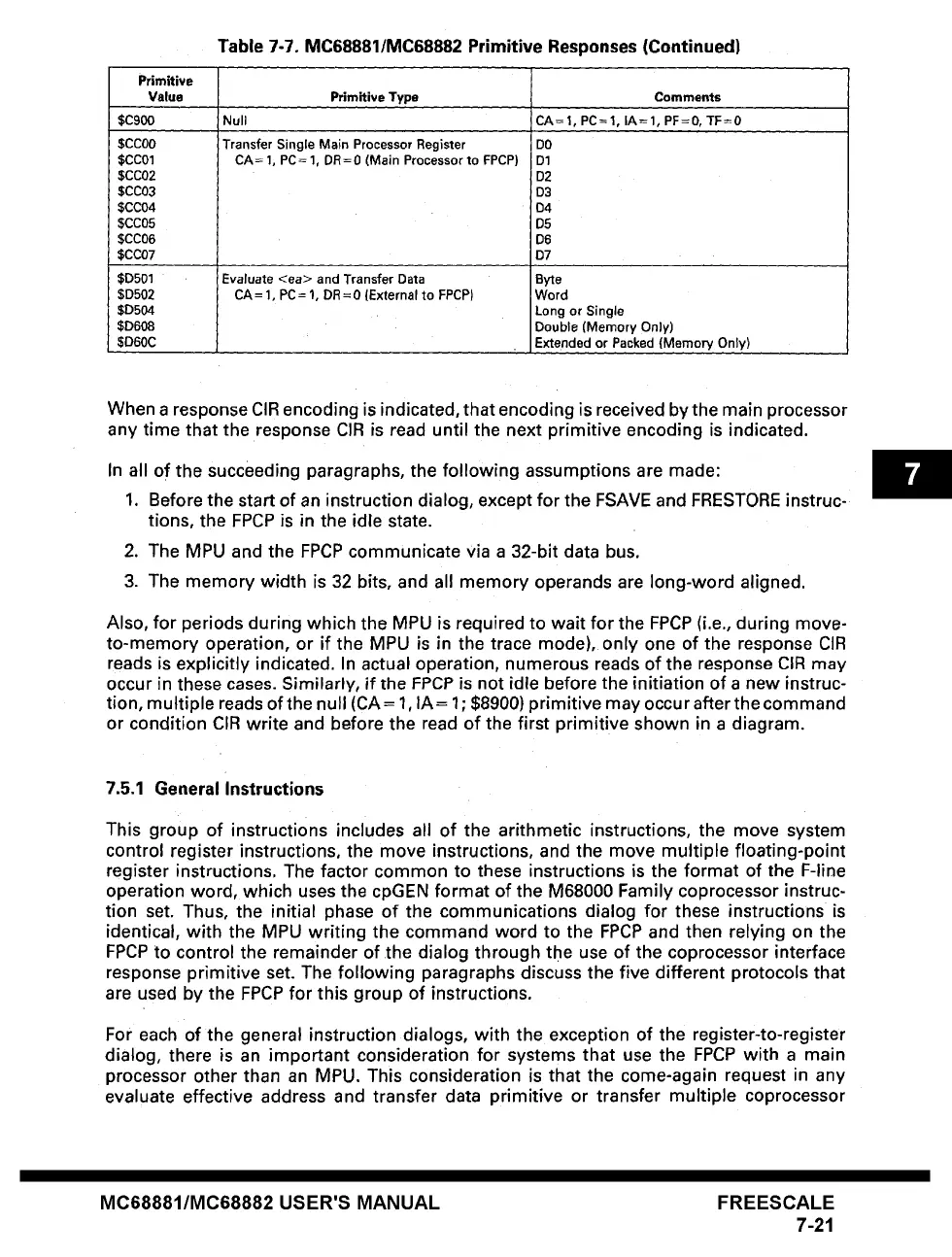

Table 7-7. MC68881/MC68882 Primitive Responses (Continued)

Primitive

Value Primitive Type Comments

$C900 Null CA=l, PC=l, IA=I, PF=0, TF=0

$CC00

$CC01

$CC02

$CC03

$CC04

$CC05

$CC06

$CC07

$D501

$D502

$D504

$D608

$D60C

Transfer Single Main Processor Register

CA= 1, PC= 1, DR=0 (Main Processor to FPCP)

Evaluate <ea> and Transfer Data

CA= 1, PC= 1, DR=0 (External to FPCP}

DO

D1

D2

D3

,D4

D5

D6

D7

Byte

Word

Long or Single

Double (Memory Only)

Extended or Packed (Memory Only)

When a response CIR encoding is indicated, that encoding is received by the main processor

any time that the response CIR is read until the next primitive encoding is indicated.

In all of the succeeding paragraphs, the following assumptions are made:

1. Before the start of an instruction dialog, except for the FSAVE and FRESTORE instruc-

tions, the FPCP is in the idle state.

2. The MPU and the FPCP communicate Via a 32-bit data bus.

3. The memory width is 32 bits, and all memory operands are long-word aligned.

Also, for periods during which the MPU is required to wait for the FPCP (i.e., during move-

to-memory operation, or if the MPU is in the trace mode), only one of the response CIR

reads is explicitly indicated. In actual operation, numerous reads of the response CIR may

occur in these cases. Similarly, if the FPCP is not idle before the initiation of a new instruc-

tion, multiple reads of the null (CA = 1, IA = 1 ; $8900) primitive may occur after the command

or condition CIR write and before the read of the first primitive shown in a diagram.

7.5.1 General Instructions

This group of instructions includes all of the arithmetic instructions, the move system

control register instructions, the move instructions, and the move multiple floating-point

register instructions. The factor common to these instructions is the format of the F-line

operation word, which uses the cpGEN format of the M68000 Family coprocessor instruc-

tion set. Thus, the initial phase of the communications dialog for these instructions is

identical, with the MPU writing the command word to the FPCP and then relying on the

FPCP to control the remainder of the dialog through the use of the coprocessor interface

response primitive set. The following paragraphs discuss the five different protocols that

are used by the FPCP for this group of instructions.

For each of the general instruction dialogs, with the exception of the register-to-register

dialog, there is an important consideration for systems that use the FPCP with a main

processor other than an MPU. This consideration is that the come-again request in any

evaluate effective address and transfer data primitive or transfer multiple coprocessor

MC68881/MC68882 USER'S MANUAL FREESCALE

7-21

Loading...

Loading...