7.5.4 Exception Processing

This group of dialogs is actually a set of special cases of the dialogs described previously;

they are grouped here for quick reference, and to simplify the preceding discussions. For

each of the exception processing dialogs, only the differences from the normal instruction

dialogs shown previously are discussed here. Also, it should be noted that these dialogs

do not include all exception processing sequences that involve the FPCP; they only include

those exceptions that are directly related to the coprocessor interface operation. For ex-

ample, main processor detected F-line exceptions are not included since no coprocessor

interface dialog occurs as part of the exception processing for this type of an exception.

The dialog for the coprocessor protocol violation exception is also omitted from the fol-

lowing diagrams. This is because these exceptions are not expected to occur during the

normal operation of a fully debugged system, and the dialog is not readily predictable

(either before or after the protocol violation occurs). By definition, the cause of the exception

for main processor detected protocol violations is a hardware failure (since the FPCP cannot

return an illegal response primitive).

For FPCP-detected protocol violations, the cause is most likely a software failure that causes

a new instruction to be initiated before the previous instruction dialog is completed. In this

case, the new instruction dialog is aborted immediately, but the previous instruction dialog

may not terminate for some time. (The previous dialog may be completed incorrectly, since

the protocol violation is never reported to the previous instruction.)

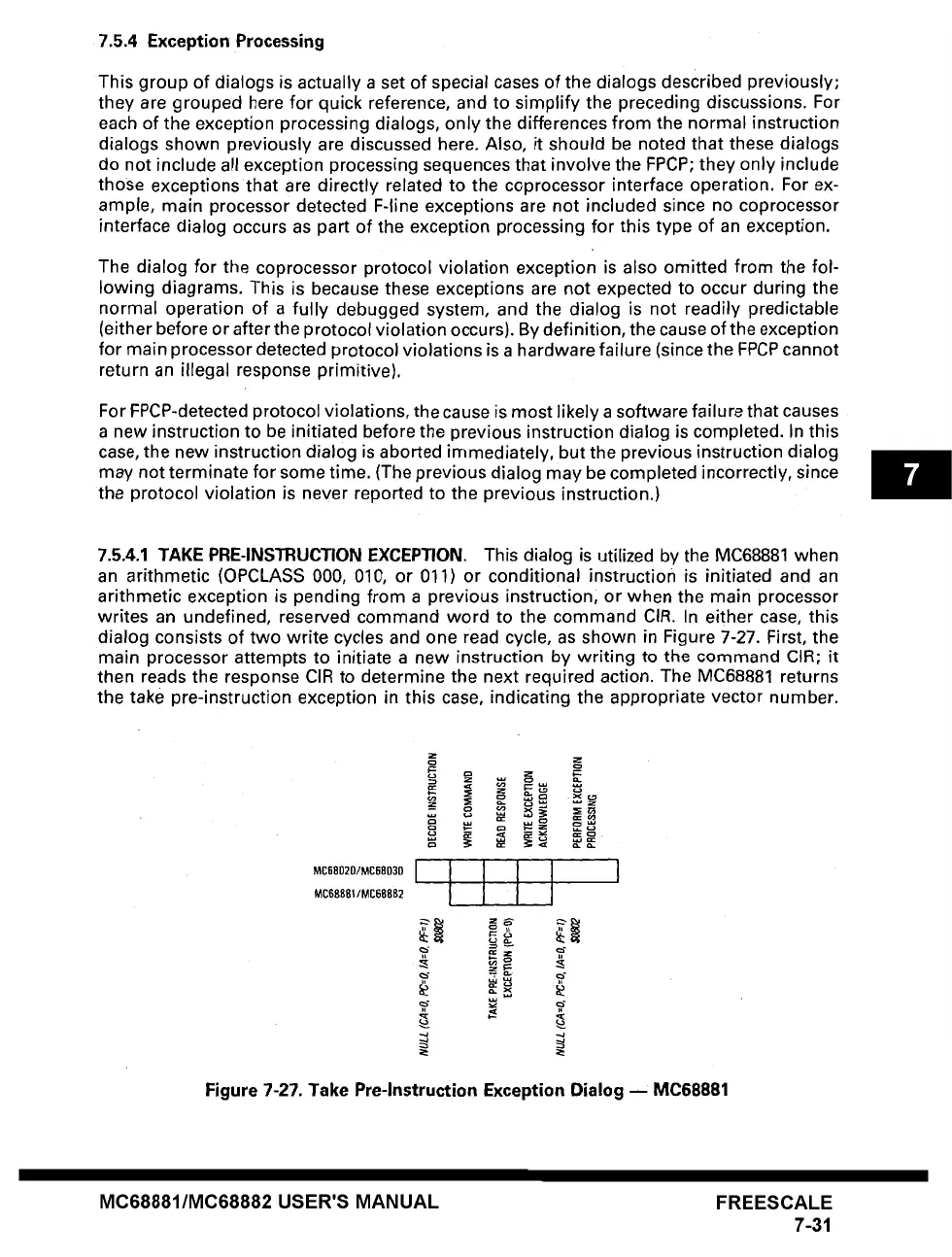

7.5.4.1 TAKE PRE-INSTRUCTION EXCEPTION. This dialog is utilized by the MC68881 when

an arithmetic (OPCLASS 000, 010, or 011) or conditional instruction is initiated and an

arithmetic exception is pending from a previous instruction; or when the main processor

writes an undefined, reserved command word to the command CIR. In either case, this

dialog consists of two write cycles and one read cycle, as shown in Figure 7-27. First, the

main processor attempts to initiate a new instruction by writing to the command CIR; it

then reads the response CIR to determine the next required action. The MC68881 returns

the take pre-instruction exception in this case, indicating the appropriate vector number.

~ == =! -

-J .u

Figure 7-27. Take Pre-lnstruction Exception Dialog m MC68881

MC68881/MC68882 USER'S MANUAL FREESCALE

7-31

Loading...

Loading...