8

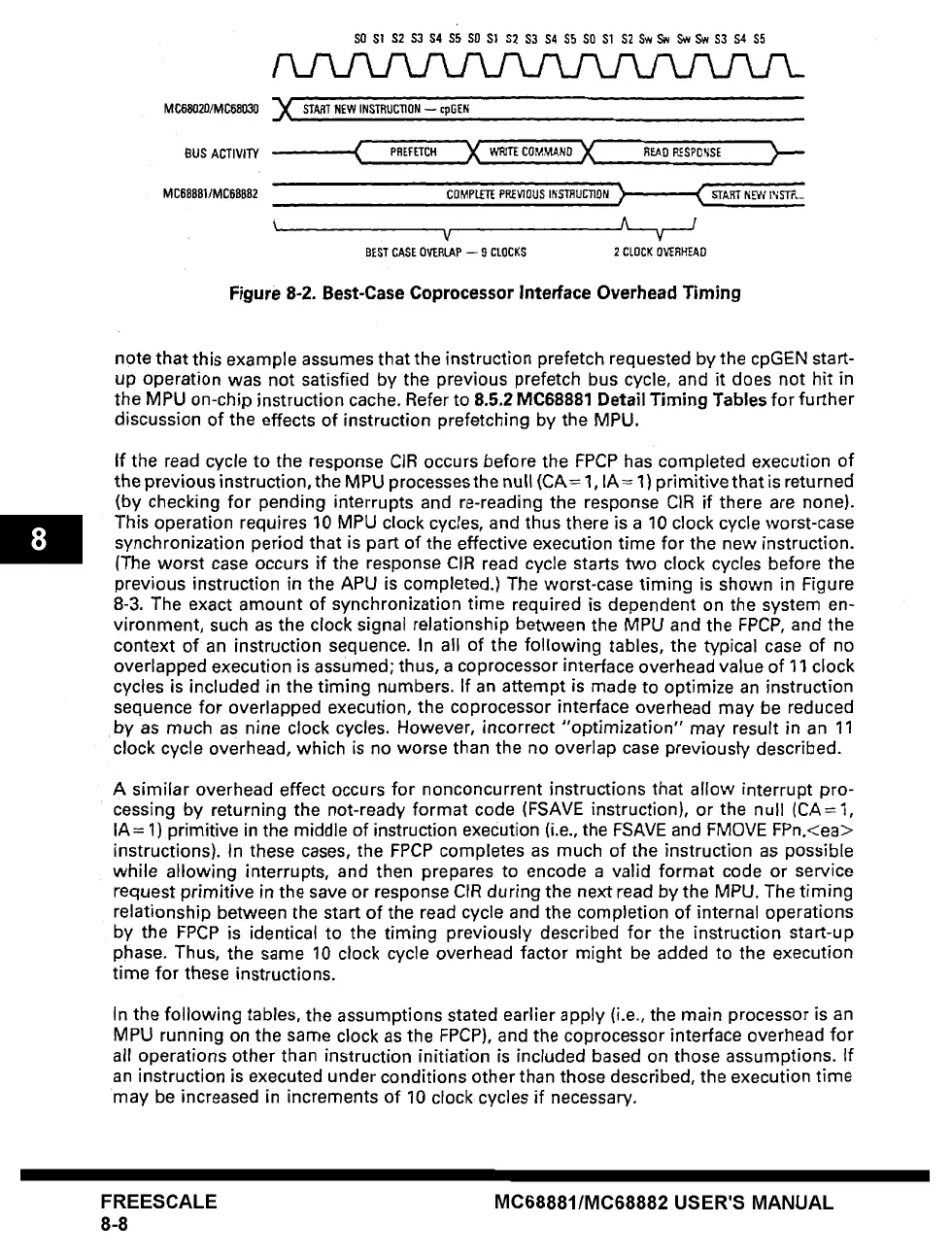

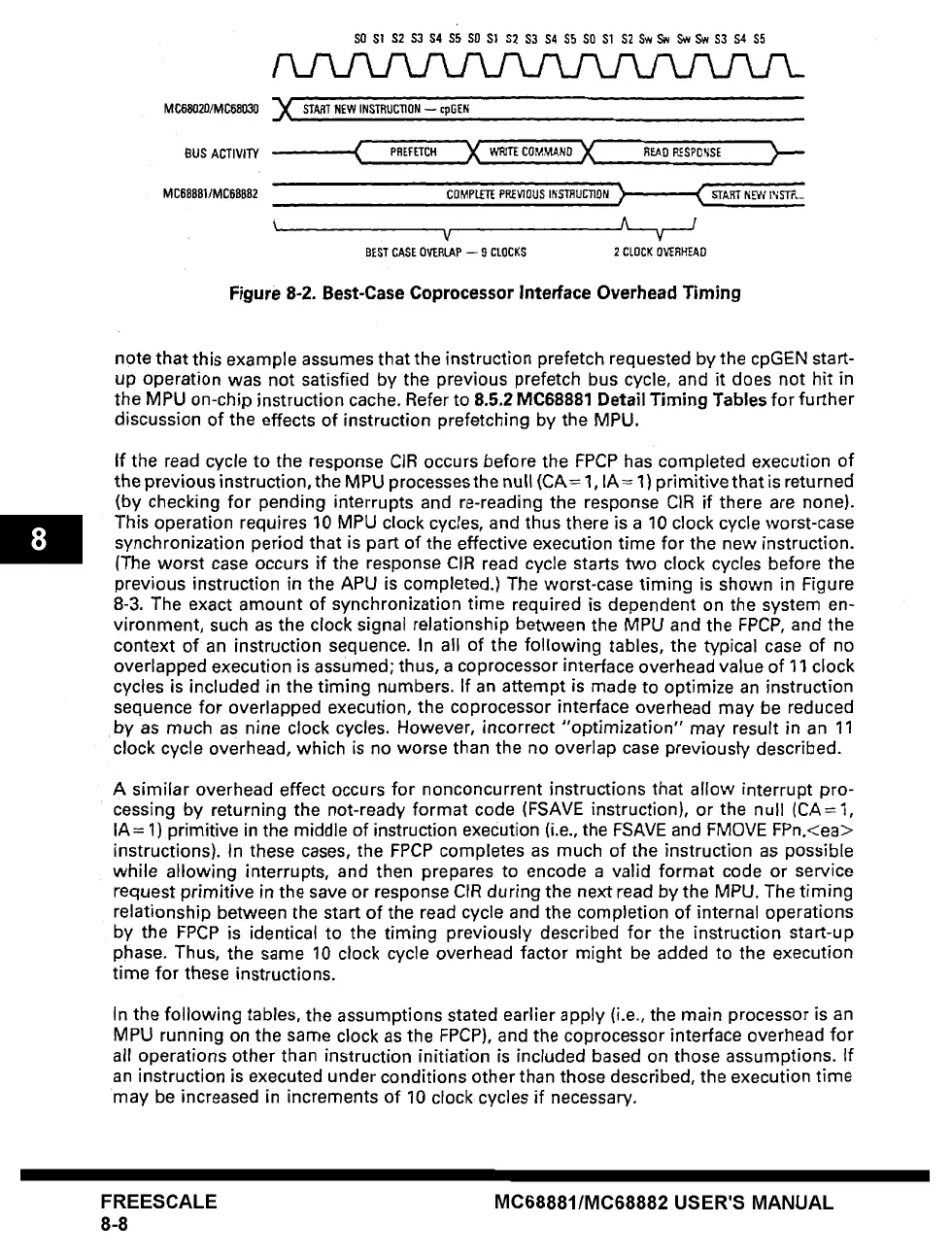

SO SI $2 $3 $4 $5 SO S] $2 $3 $4 $5 SO $1 $2 Sw Sw Sw Sw S3 St, Sfi

MC68020/MC68030 ~ START NEW INSTRUC~ON -- cpGEN

BUS ACTIVITY

MC68881]MC68882

~/ A V__/

BEST CASE OVERLAP -- 9 CLOCKS 2 CLOCK OVERHEAD

Figure 8-2. Best-Case Coprocessor Interface Overhead Timing

note that this example assumes that the instruction prefetch requested by the cpGEN start-

up operation was not satisfied by the previous prefetch bus cycle, and it does not hit in

the MPU on-chip instruction cache. Refer to 8.5.2 MC68881 Detail Timing Tables for further

discussion of the effects of instruction prefetching by the MPU.

If the read cycle to the response CIR occurs before the FPCP has completed execution of

the previous instruction, the MPU processes the null (CA= 1, IA= 1) primitive that is returned

(by checking for pending interrupts and re-reading the response CIR if there are none).

This operation requires 10 MPU clock cycles, and thus there is a 10 clock cycle worst-case

synchronization period that is part of the effective execution time for the new instruction.

(The worst

case occurs if the response CIR read cycle starts two clock cycles before the

previous instruction in the APU is completed.) The worst-case timing is shown in Figure

8-3. The exact amount of synchronization time required is dependent on the system en-

vironment, such as the clock signal relationship between the MPU and the FFCP, and the

context of an instruction sequence. In all of the following tables, the typical case of no

overlapped execution is assumed; thus, a coprocessor interface overhead value of 11 clock

cycles is included in the timing numbers. If an attempt is made to optimize an instruction

sequence for overlapped execution, the coprocessor interface overhead may be reduced

by as much as nine clock cycles. However,

incorrect "optimization" may result in an 11

clock cycle overhead, which is no worse than the no overlap case previously described.

A similar overhead effect occurs for nonconcurrent instructions that allow interrupt pro-

cessing by returning the not-ready format code (FSAVE instruction), or the null (CA = 1,

IA= 1) primitive in the middle of instruction execution (i.e., the FSAVE and FMOVE FPn,<ea>

instructions). In these cases, the FPCP completes as much of the instruction as possible

while allowing interrupts, and then prepares to encode a valid format code or service

request primitive in the save or response CIR during the next read by the MPU. The timing

relationship between the start of the read cycle and the completion of internal operations

by the FPCP is identical to the timing previously described for the instruction start-up

phase. Thus, the same 10 clock cycle overhead factor might be added to the execution

time for these instructions.

In the following tables, the assumptions stated earlier apply (i.e., the main processor is an

MPU running on the same clock as the FPCP), and the coprocessor interface overhead for

all operations other than instruction initiation is included based on those assumptions. If

an instruction is executed under conditions other than those described, the execution time

may be increased in increments of 10 clock cycles if necessary.

FREESCALE

8-8

MC68881/MC68882 USER'S MANUAL

Loading...

Loading...