4

FDIV

Divide

FDIV-

Operation: FPn (+) Source J FPn

Assembler

FDIV.<fmt> <ea>,FPn

Syntax:

FDIV.X FPm,FPn

Attributes: Format= (Byte, Word, Long, Single, Double, Extended, Packed)

Description:

Converts the source operand to extended precision (if necessary) and di-

vides that number into the number in the destination floating-point data register.

Stores the result in the destination floating-point data register.

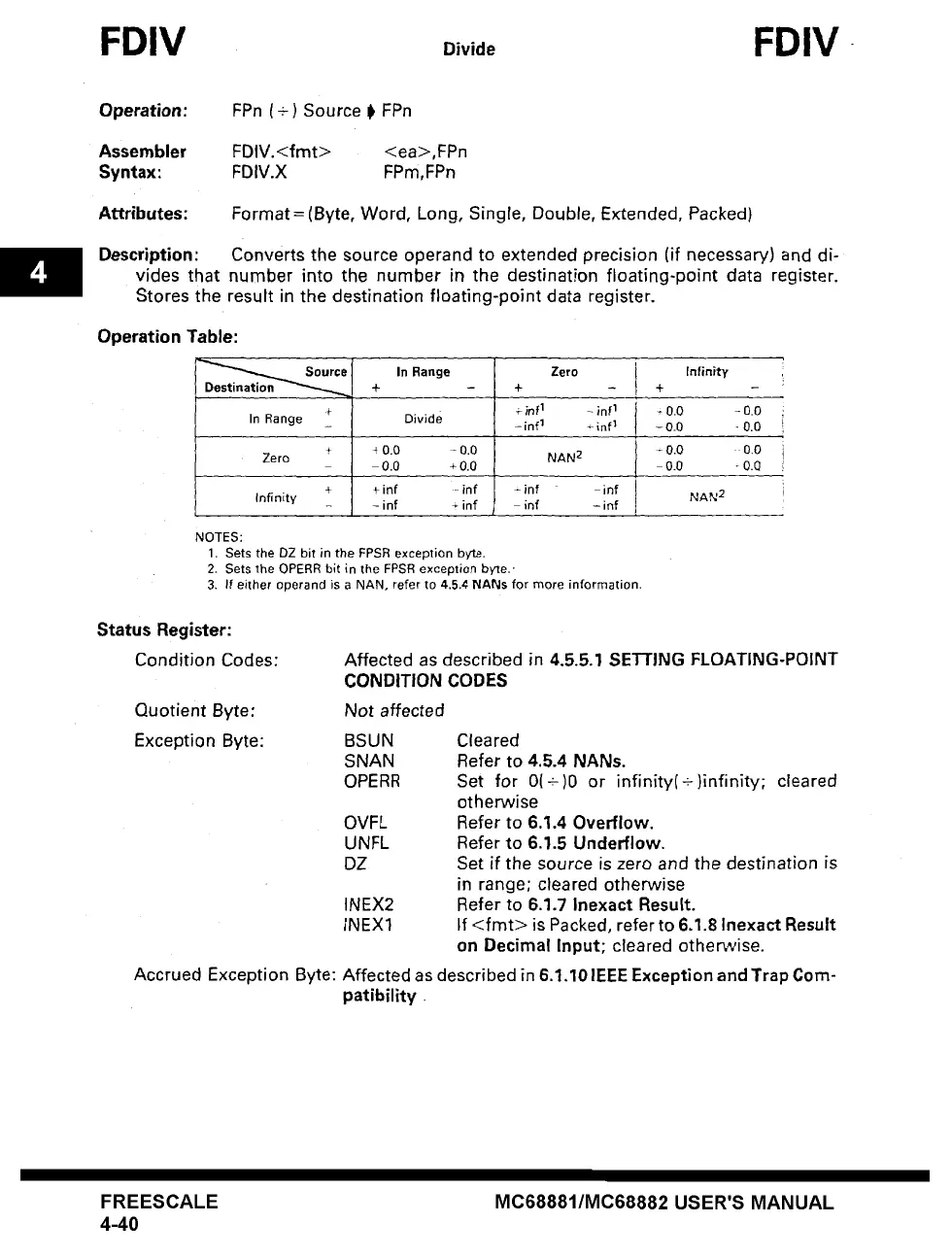

Operation Table:

Source:

Destination

~

In Range

+

Zero

+

Infinity

In Range

+

Divide

40.0 -0.0

0.0 +0.0

finf -inf

-inf + inf

Zero

+

+inf 1 -inf 1

-inf 1 +infl

NAN 2

inf - -inf

inf -inf

Infinity

+

I + 0.0 - O.0

• -0.0 -

0.0

l ~0.0 0.0

0.0 - 0.Q

NAN 2

NOTES:

1. Sets the DZ bit in the FPSR exception byte.

2, Sets the OPERR bit in the FPSR exception byte."

3, If either operand is a NAN, refer to 4.5,4 NANs for more information.

Status Register:

Condition Codes:

Quotient Byte:

Exception Byte:

Accrued Exception Byte:

Affected as described in 4.5.5.1 SETTING FLOATING-POINT

CONDITION CODES

Not affected

BSUN

SNAN

OPERR

OVFL

UNFL

DZ

tNEX2

INEX1

Cleared

Refer to 4.5.4 NANs.

Set for 0(+)0 or infinity(÷)infinity; cleared

otherwise

Refer to 6.1.4 Overflow.

Refer to 6.1.5 Underflow.

Set if the source is zero and the destination is

in range; cleared otherwise

Refer to 6.1.7 Inexact Result.

If <fret> is Packed, refer to 6.1.8 Inexact Result

on

Decimal Input; cleared otherwise.

Affected as described in 6.1.10 IEEE Exception and Trap Com-

patibility

FREESCALE

4-40

MC68881/MC68882 USER'S MANUAL

Loading...

Loading...