FDIV

Divide

FDIV

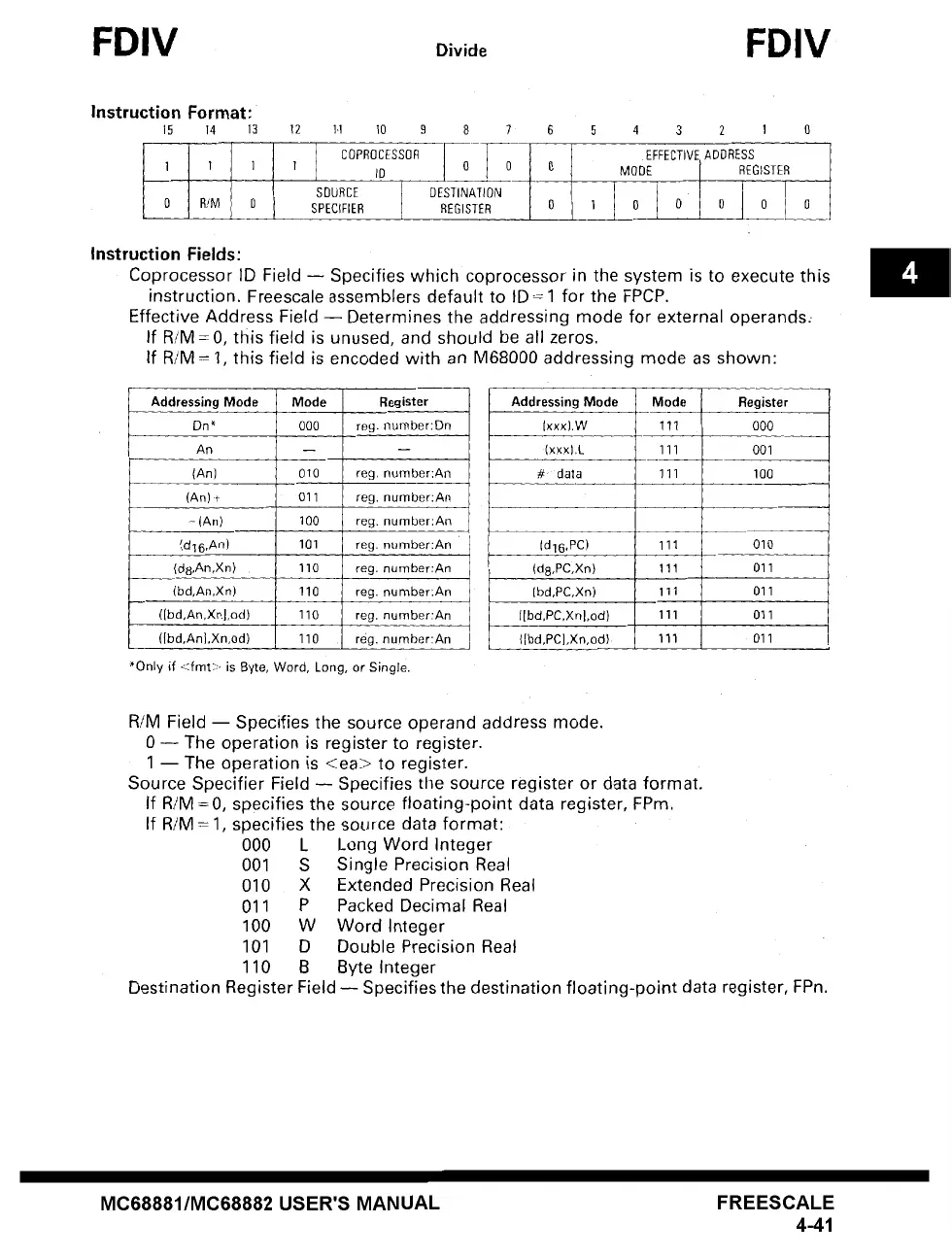

Instruction Format:

15 14 13 H ]0 9 8 7 6 5 4 3 2 1

1 1 ID 0 MODE REGISTER

SOURCE DESTINATION

0

R/M SPECIFIER L REGISTER

0 1 O 0 0 O g

Instruction Fields:

Coprocessor ID Field -- Specifies which coprocessor in the system is to execute this

instruction. Freescale assemblers default to ID-- 1 for the FPCP.

Effective Address Field -- Determines the addressing mode for external operands..

If R/M=0, this field is unused, and should be all zeros.

If R/M= 1, this field is encoded with an M68000 addressing mode as shown:

Addressing Mode

Dn ~

An

(An)

(An) t

-(An)

(dlG,An)

(ds,An,Xn)

{bd,An,Xn)

([bd,An,XnJ,od)

([bd,AnJ,Xn,od)

Mode Register

000 reg.

number:Dn

010 reg, number:An

011 reg. number:An

100 I reg, number:An

101 reg. number:An

110 reg. number:An

110 reg. number:An

110 reg. number:An

110 reg. number:An

*Only if <fmt>

is Byte, Word, Long, or Single•

Addressing Mode Mode

(xxx),W

111

(xxx),L 111

# data 111

(d16,PC) 111

(ds,PC,Xn) 111

(bd,PC,Xn) 111

([bd,PC,Xnl,od) 111

{[bd,PC],Xn,od) 111

Register

0O0

001

100

01O

011

Oll

011

011

R/M Field -- Specifies the source operand address mode.

0 -- The operation is register to register.

1 -- The operation is <ea> to register.

Source Specifier Field -- Specifies the source register or data format.

If R/M = 0, specifies the source floating-point data register, FPm,

If R/M = 1, specifies the source data format:

000 L

001 S

010 X

011 P

100 W

101 D

110 B

Destination Register Field

Long Word Integer

Single Precision Real

Extended Precision Real

Packed Decimal Real

Word Integer

Double Precision Real

Byte Integer

-- Specifies the destination floating-point data register, FPn.

MC68881/MC68882 USER'S MANUAL FREESCALE

4-41

Loading...

Loading...