BIOS Error Handling ESB2 BMC Core TPS

Revision 1.0

Intel order number E18291-001

228

This uncorrectable error message is propagated upstream to the root port and signaled as an

SERR in the PCI Status register on the primary side of bridge device. Our PCI error handler

detects the PERR event on the downstream device and an SERR event on the primary side of

the bridge and all upstream agents to the root port.

The server system does not support embedded PCI Express to PCI-X* bridges or PCI-X slots.

The only case in which this situation might be encountered is for a PCI Express* adapter card

using a PCI Express* to PCI-X* bridge onboard the adapter with a PCI-X* device behind the

bridge. This is quite common in early generation PCI Express* devices.

PCI Express* correctable error messages are not reported by the BIOS. These errors are

scrubbed by chipset and/or device hardware and there is no need to report them in the absence

of any frequency monitoring software that provides fault prediction analysis.

19.2.2.5 Sensor Events/Errors

The BMC manages sensors. It can receive event messages from individual sensors and logging

system events.

19.2.3 System Event Logging (SEL) Format Conventions

The BIOS complies with the logging format defined in the Intelligent Platform Management

Interface Specification, Version 2.0. See Table 32-1, SEL Event Records. This section

describes the format used by the BIOS to create SEL entries for reporting certain system errors

and events.

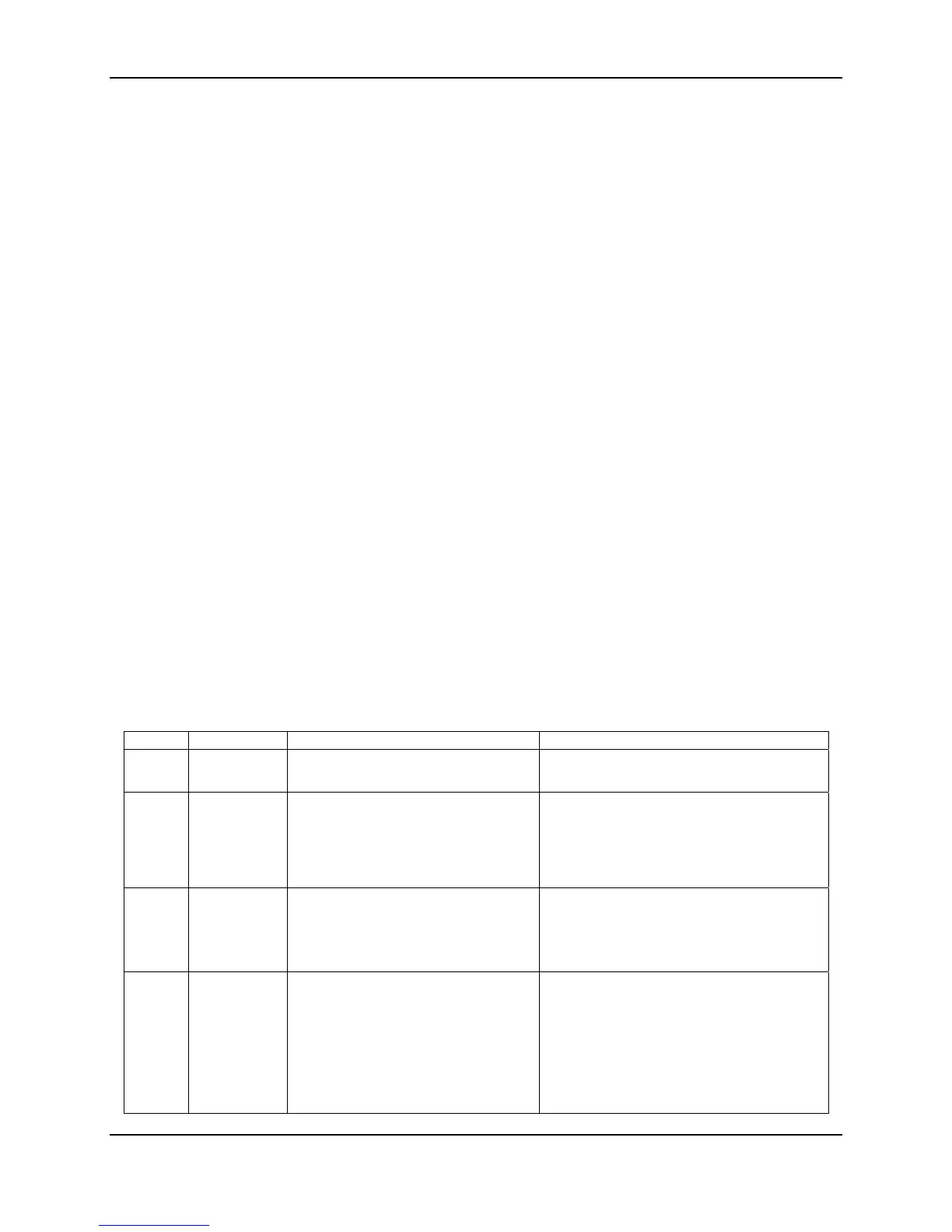

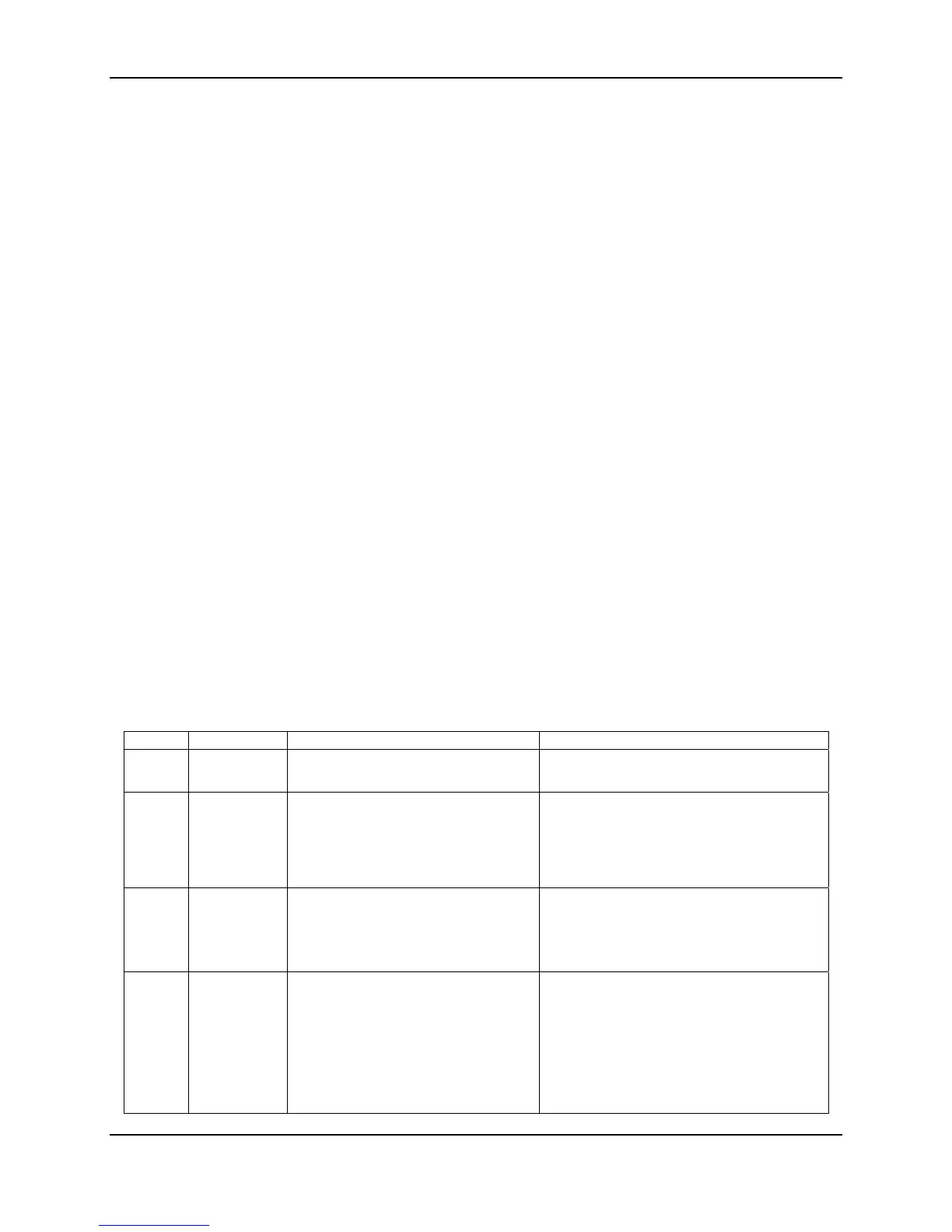

The following table indicates standard header fields common to all SEL entries that the BIOS

logs:

Table 83. SEL Entry Format — Generic Fields

Byte Field IPMI Description BIOS Implementation

1

2

Record ID ID used for SEL record access. The BMC logs unique Record ID.

3 Record Type Bit[7:0] = Record Type

02h = system event record

C0h–DFh = OEM, Byte 8-16

E0h–FFh = OEM, Byte 4-16

The BIOS sends this to the BMC:

Bit[7:0] Record Type = 02h

Currently all SEL entries logged as

standard IPMI System Event Record

entries

4

5

6

7

Timestamp Time when event was logged

LS byte first

The BMC logs timestamp value.

8

9

Generator

ID

Byte 8

Bit[7:1] = System software ID or

IPMB slave address.

Bit[0]

0b = IPMB slave address

1b = System Software ID

Byte 9

The BIOS sends this to the BMC:

Byte 8 = 0x33:

Bit[7:4] System Software ID (SSID)

0011b = BIOS SMI Error Handler

ID

Bit[3:1] Custom sub-field

Loading...

Loading...