Intel® Server System S7000FC4UR TPS BIOS Role in Server Management

Revision 1.0

219

18.5.3.17 Type 38 Structure — IPMI Device Information

The SMBIOS Type 38 structure describes the attributes of the embedded IPMI controller on the

server board. In addition to the System Management BIOS Reference Specification, Version 2.5

requirements, two bytes have been appended to the Type 38 structure to provide the following:

Information about the interrupt used by embedded IPMI controller

More information about the IPMI base address

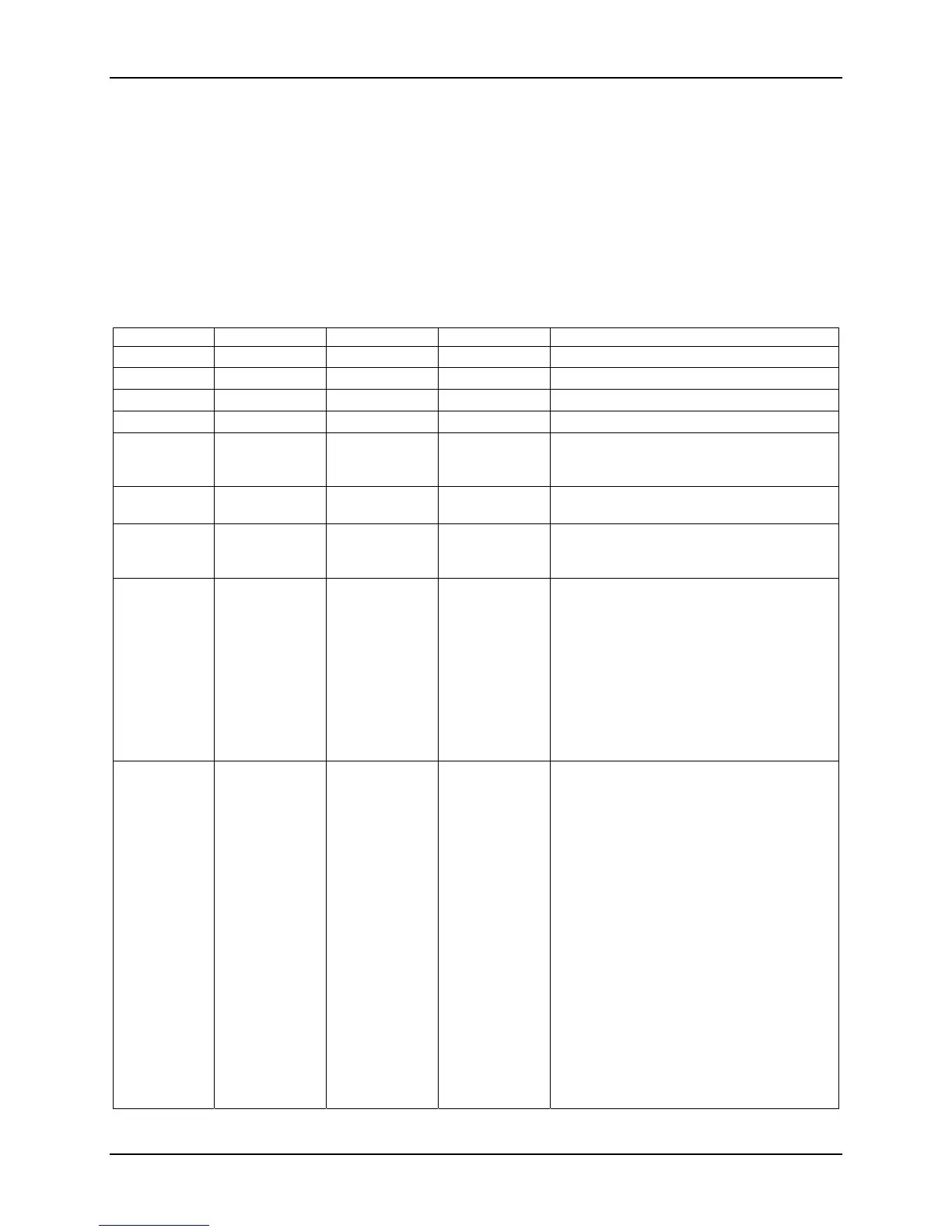

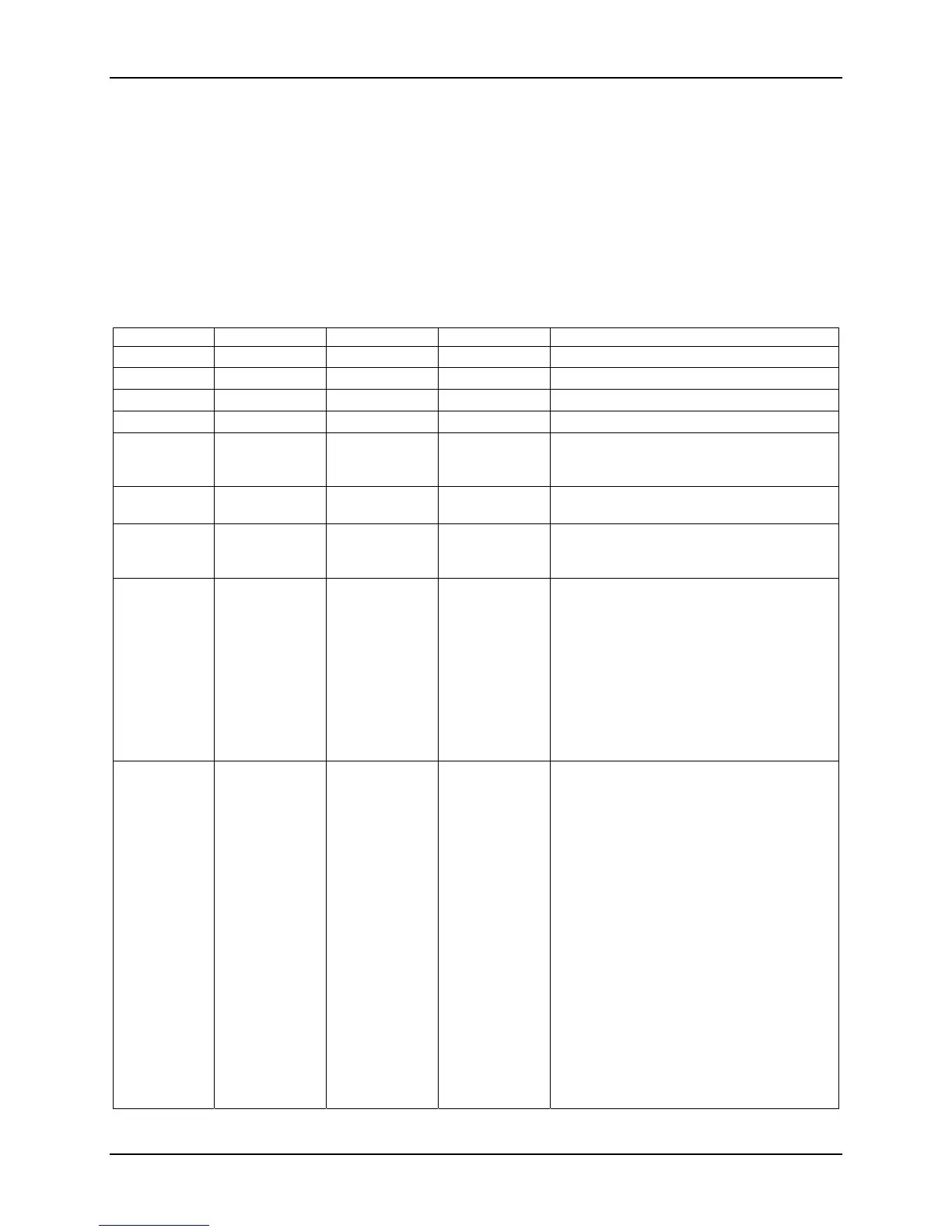

Table 81. SMBIOS Type 38 Structure — IPMI Device Information

Offset Name Length Value Description

00h Type Byte 38 IPMI device information structure indicator.

01h Length Byte 12h

02h Handle Word Varies

04h Interface Type Byte 01h 01h = KCS Interface.

05h IPMI

Specification

Revision

Byte 20h IPMI Specification, Version 2.0.

06h I

2

C Slave

Address

Byte Varies Slave address of the I

2

C bus

07h NV Storage

Device

Address

Byte Varies Bus ID of the non-volatile storage device.

08h Base Address QWord Varies The base address for the BMC’s system

interface. The field can describe both I/O

mapped and memory-mapped base

addresses. The least significant bit

indicates whether the base address is an

I/O address or a memory address. The

most significant 63 bits holds the most

significant 63 bits (bits 63:1) of a 64-bit

address. The least significant bit (bit 0) of

the base address is kept in the Base

Address Modifier field.

10h Base Address

Modifier /

Interrupt Info

Byte Varies Base address modifier:

Bit 7:6 Register spacing

00b = interface registers are on

successive byte boundaries

01b = interface registers are on 32-bit

boundaries

10b = interface registers are on 16-

byte boundaries

11b = reserved

Bit 5

Reserved: Return as 0b

Bit 4 LS-bit for addresses

0b = Address bit 0 = 0b

1b = Address bit 0 = 1b

Interrupt information identifies the

type and polarity of the interrupt

associated with the IPMI system

interface, if any.

Loading...

Loading...