Intel® Server System S7000FC4UR Hot-Swap Controller (HSC) Architecture

Revision 1.0

301

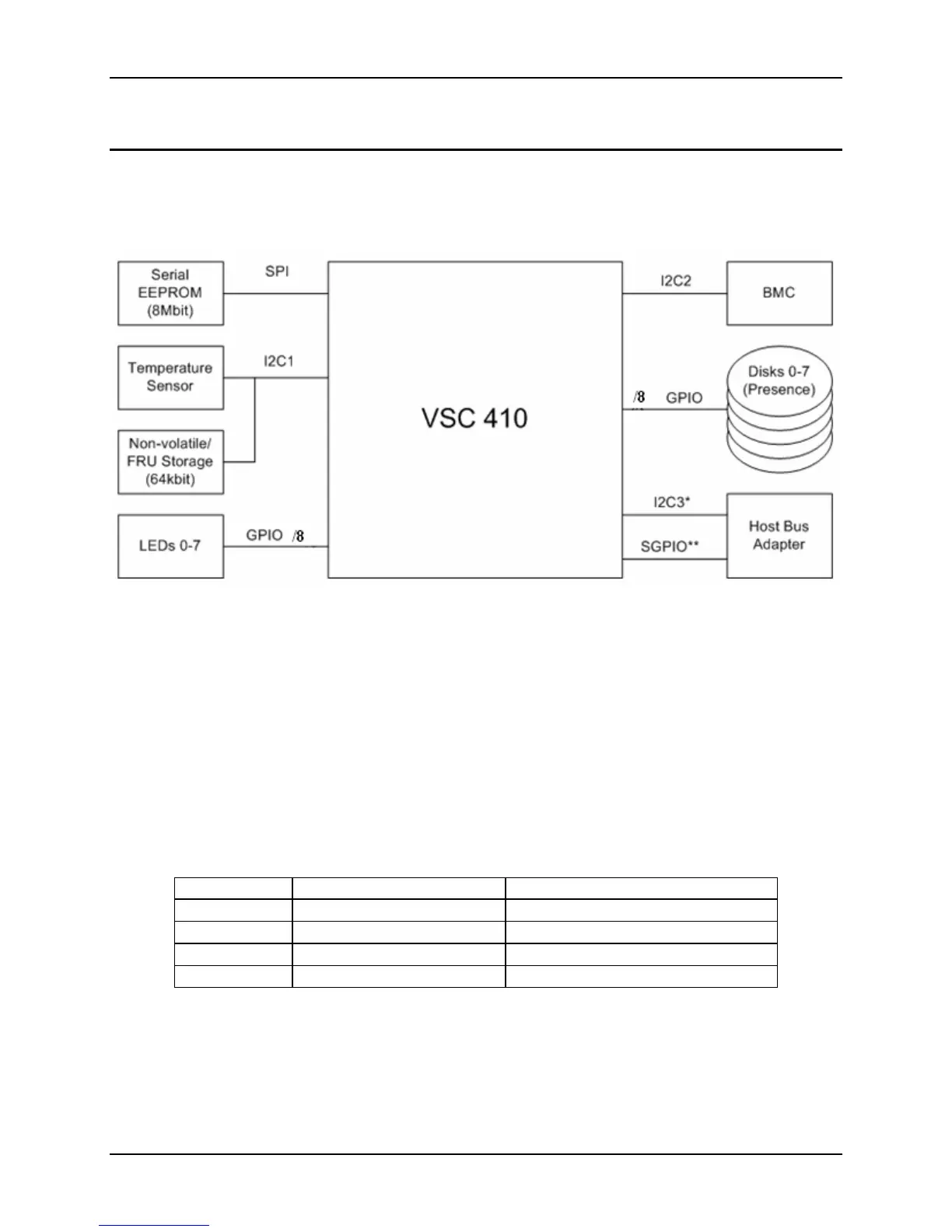

28. Hot-Swap Controller (HSC) Architecture

The HSC uses a VSC410* SAF-TE enclosure processor (SEP). This microcontroller employs a

v3000 RISC CPU, 8 KB of internal SRAM, GPIO, SGPIO, two general purpose UARTs, one

SPI, and four I

2

C compatible interfaces.

Figure 71. HSC Interface Routing

* If present, SGPIO is disconnected.

** If present, I2C3 is disconnected.

28.1.1 I

2

C Interfaces

The VSC410 supports four I

2

C compatible serial interfaces. These multi-master interfaces are

configured in firmware to operate at 100 KHz. Optional support functions, such as I

2

C bus

cleanups, can be configured in firmware.

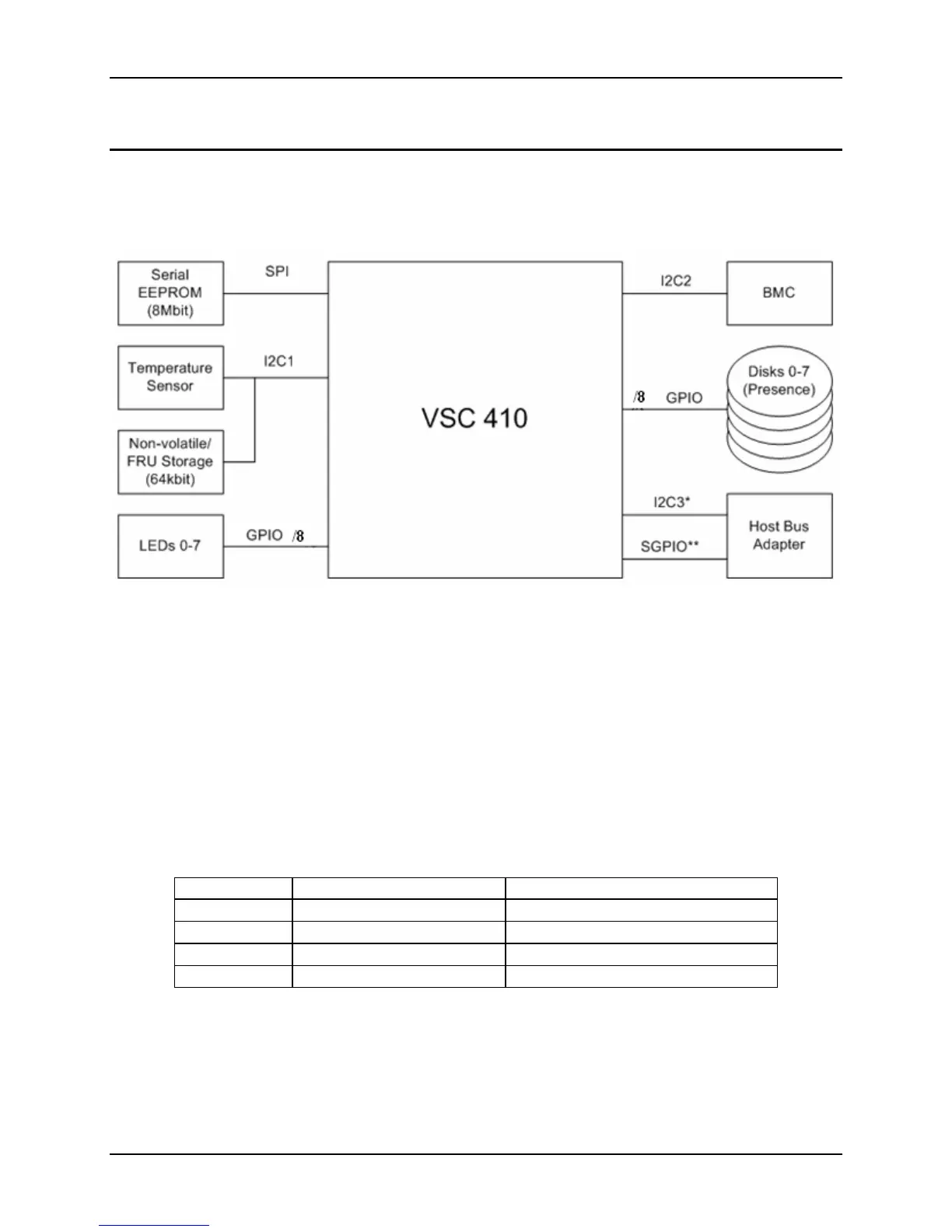

Table 105. I

2

C Bus Assignements

I

2

C Bus Number Connection Protocol Connected Device(s)

I2C0 Reserved None

I2C1 Master / slave I

2

C (private bus) Temperature sensor, NV/FRU EEPROM

I2C2 IPMB Baseboard management controller

I2C3 SES2-over-I

2

C, SAFTE Host bus adapter

28.1.2 Serial Peripheral Interface (SPI)

The VSC410 SPI accesses operational code in a separate SPI-compatible EEPROM device.

This interface is private and can only be accessed by the HSC to retrieve or update firmware.

Loading...

Loading...