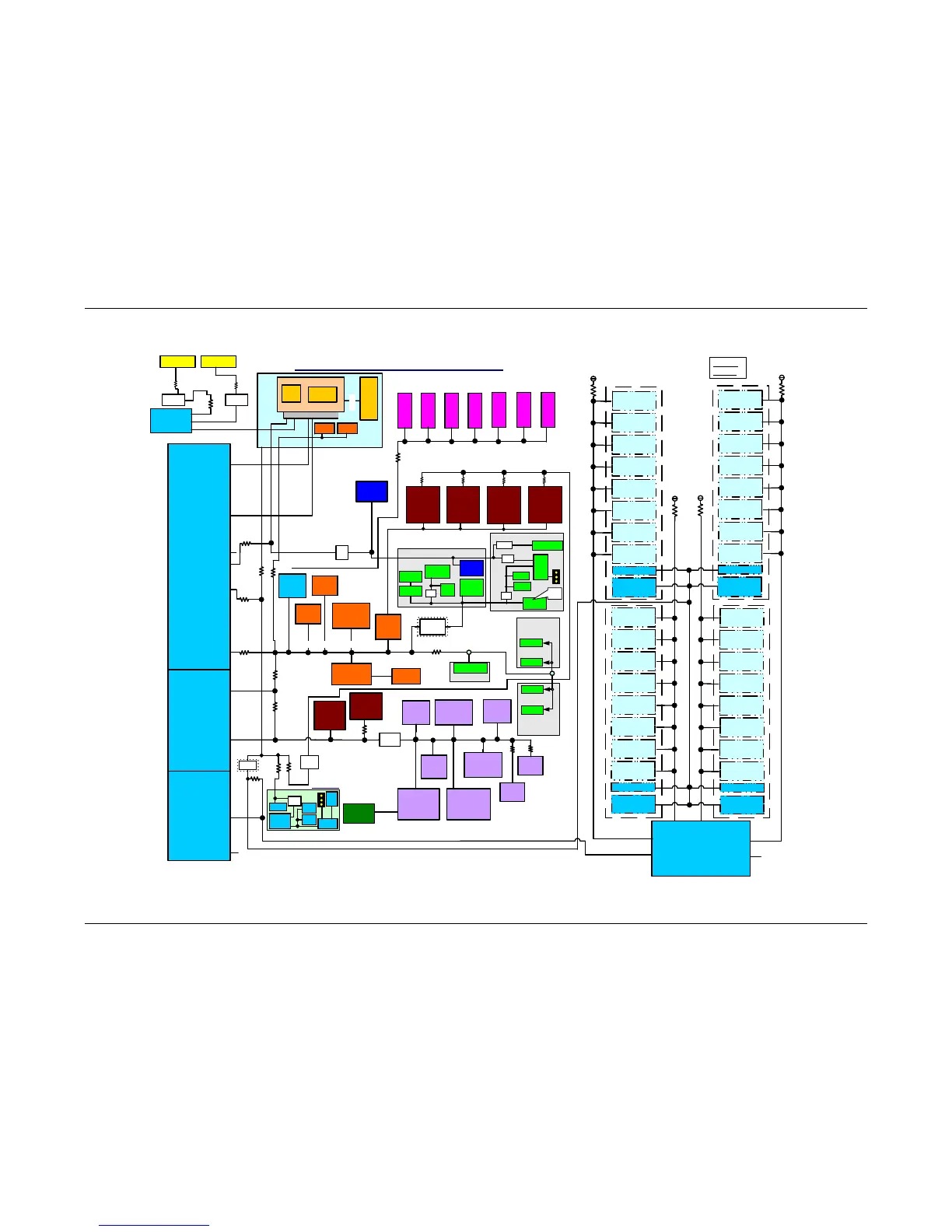

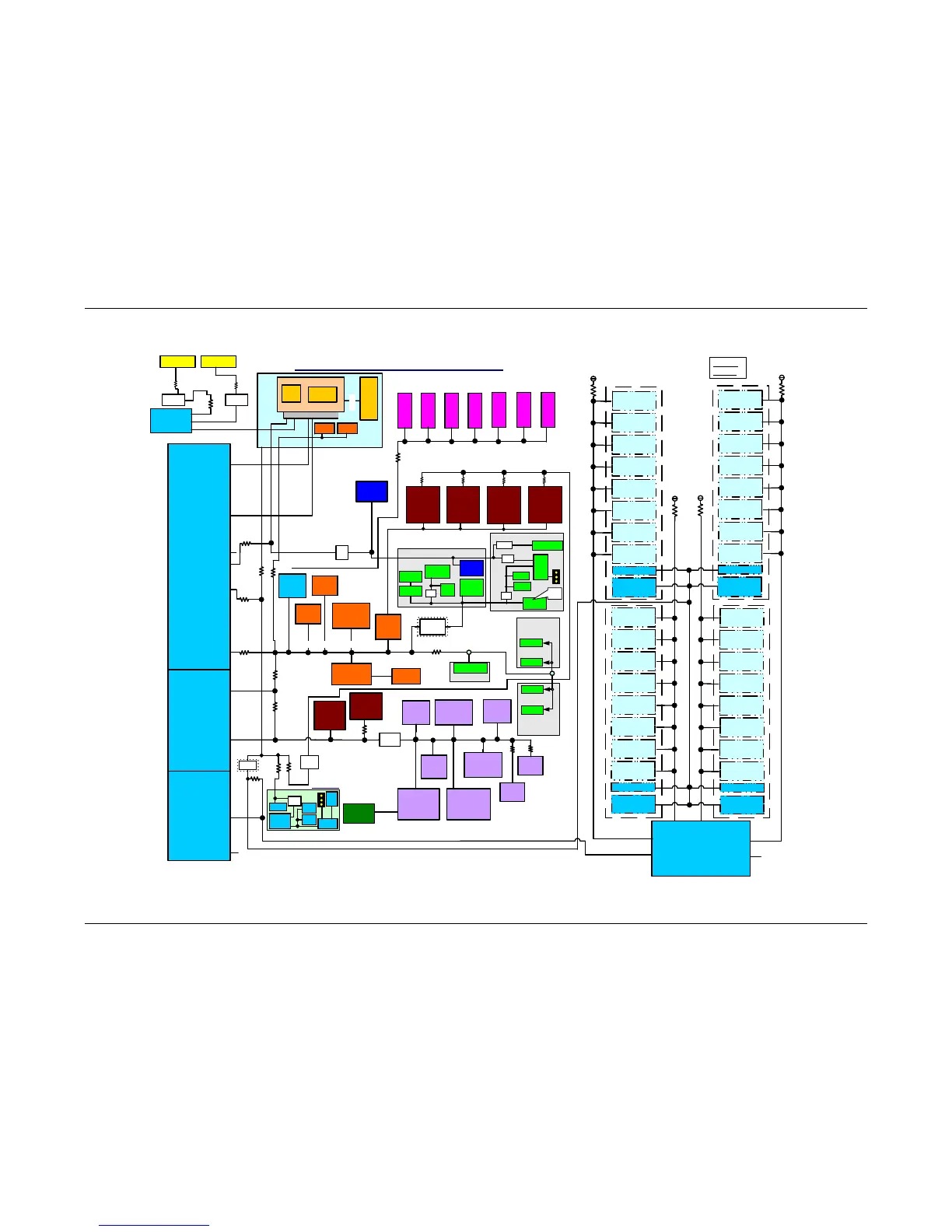

3.2.2 SMBus Block Diagram

BMC

ICH6

PEXH

Power Supply #2

FRU

Addr: 0xAE

Transaction over FML0 (ESB2 is slave)

Transaction over FML1 (ESB2 is master)

PC87427 (SIO3)

(Addr: 0xD8)

TMP141

Ambient Temp

(Addr: 0x02)

Memory Riser A

Clarksboro

CFGSMBDATA/CFGSMBCLK

(Slave, 100KHz, 0xC0)

FRU: Addr A4

NE1617

Temp Sensor

(Addr: 0x34)

DIMM A1

SEEPROM 0xA0

AMB 0xB0

DIMM A2

SEEPROM 0xA2

AMB 0xB2

DIMM A3

SEEPROM 0xA4

AMB 0xB4

DIMM A4

SEEPROM 0xA6

AMB 0xB6

DIMM A5

SEEPROM 0xA8

AMB 0xB8

DIMM A6

SEEPROM 0xAA

AMB 0xBA

DIMM A7

SEEPROM 0xAC

AMB 0xBC

DIMM A8

SEEPROM 0xAE

AMB 0xBE

3V3

3V3

Memory Riser B

FRU: Addr A6

DIMM B1

SEEPROM 0xA0

AMB 0xB0

DIMM B2

SEEPROM 0xA2

AMB 0xB2

DIMM B3

SEEPROM 0xA4

AMB 0xB4

DIMM B4

SEEPROM 0xA6

AMB 0xB6

DIMM B5

SEEPROM 0xA8

AMB 0xB8

DIMM B6

SEEPROM 0xAA

AMB 0xBA

DIMM B7

SEEPROM 0xAC

AMB 0xBC

DIMM B8

SEEPROM 0xAE

AMB 0xBE

3V3

FRU: Addr A0

DIMM D1

SEEPROM 0xA0

AMB 0xB0

DIMM D2

SEEPROM 0xA2

AMB 0xB2

DIMM D3

SEEPROM 0xA4

AMB 0xB4

DIMM D4

SEEPROM 0xA6

AMB 0xB6

DIMM D5

SEEPROM 0xA8

AMB 0xB8

DIMM D6

SEEPROM 0xAA

AMB 0xBA

DIMM D7

SEEPROM 0xAC

AMB 0xBC

DIMM D8

SEEPROM 0xAE

AMB 0xBE

3V3

Memory Riser C

FRU: Addr A2

DIMM C1

SEEPROM 0xA0

AMB 0xB0

DIMM C2

SEEPROM 0xA2

AMB 0xB2

DIMM C3

SEEPROM 0xA4

AMB 0xB4

DIMM C4

SEEPROM 0xA6

AMB 0xB6

DIMM C5

SEEPROM 0xA8

AMB 0xB8

DIMM C6

SEEPROM 0xAA

AMB 0xBA

DIMM C7

SEEPROM 0xAC

AMB 0xBC

DIMM C8

SEEPROM 0xAE

AMB 0xBE

SPD0SMBDATA/CLK

(Master SPD, 100KHz)

SPD2SMBDATA/CLK

(Master SPD, 100KHz)

SPD1SMBDATA/CLK

(Master SPD, 100KHz)

SPD3SMBDATA/CLK

(Master SPD, 100KHz)

3.3V

3.3V

3.3V 3.3V

3.3V

Not used

SMBCLK/SMBDATA

(Master)

Addr 0x44

3V3

DB1900G

(0xDA)

FBD, Branch1

SMB_1_3V3SB_MS_*

SMB_0_3V3SB_MS_*

Note:

1) * in the netnames represents CLK and DAT

2) Hot-plug isolation details for PCIe SMBusses & SMBus pull-ups are not shown in this diagram. SMBus Alert# signal connectivity is also not shown in the

diagram for simplicity. SMBus alert# from a SMBus should be connected to devices on that SMBus if the devices on that SMBus have SMBus Alert# signal.

3) Pull-up values, # of repeaters required for SMBusses will be calculated by using SMBus pull-up calculation BKM.

SMB_CLK_IO_3V3SB_*

SMB_CHIPSET_3V3_*

5VSTBY

SMB_IPMB_*

RMM2/ASMI

Tyco 5H Receptacle 120 pins

(P/N: 177983-5)

Tyco 8H P lug 120 pins

(P/N: 179031-5)

BMC

IPMB

0x26

FPGA

0x30 (MS)

0x32 (SL)

GCM3 PHY

(General Communications

Module #3)

Intel IO Riser

89HPES24N3A

(PCIe Expander)

Slot # 3 & 4

SSMBDAT/SSMBCLK

(Addr: 0xE2)

89HPES24N3A Slave SMBus

supports ARP (SMBus

address resolution protocol)

LM94

(1)

(Addr: 0x5C)

LM94

(2)

(Addr: 0x58)

Dynamic Bus Addressing for PCIe Slots (i.e. PCIe

slots support SMBus address resolution protocol)

PCI Express

Slot (Slot #2)

Hot-Plug Capable

PCI Express

Slot (Slot #3)

PCI Express

Slot (Slot #1)

Hot-Plug Capable

PCI Express

Slot (Slot #4)

PCI Express

Slot (Slot #5)

PCI Express

Slot (Slot #6)

PCI Express

Slot (Slot #7)

2.5" SAS Backplane

SMB_IPMB_5VSB_*

NON INTEL

LCD Module

Addr: 0xDA

LM75

Addr: 0x98

USB HUB

USB20H04D

Addr: 0x5A

INTEL LCD

Module

Addr: 0x22

Intel® SR 4851HW4 Front Panel

Level

Shift

SensorPath

3V3

DB1900G

(0xD4)

PCIE

SMBus

Isolation

Baseboard

IPMB HDR

SMB_PCIE_3V3SB_*

CPU # 4

EEPROM

(SMB Addr: AE)

CPU # 3

EEPROM

(SMB Addr: AC)

CPU # 2

EEPROM

(SMB Addr: AA)

CPU # 1

EEPROM

(SMB Addr: A8)

RN50

GPIO[6:5]

VID_DVO_DDC_*

VGADDCDAT/

VGADDCCLK

Rear Video

Connector

ADT7490

PECI

Device

(Addr: 0x5A)

S7000FC4UR SMBus Block Diagram

Front Panel

Connector

3V3

XDP2

(Chipset)

SMBus

Master Only

0-ohm

(empty)

3V3

XDP1 (CPUs)

SMBus

Master Only

0-ohm

(empty)

SMB_SYS_BRD_*

Memory Riser D

SMB_MEM_3V3_*

Rev 2.1

1/26/07

3.3V

0-ohm

empty

SMB_CLK_IO_3V3_*

MII

BMC GPIO

Expander

PCA9555

(Addr: 0x40)

CPU_PECI_IO

Note: ESB2 BMC does not

act as a SMBus ARP

master.

SMB_BB_SENSOR_3V3SB_*

Note: CPU_PECI_IO is a

PECI and not a SMBus

FRU

Addr: 0xA8

LM75

Addr: 0x96

Power Supply #1

FRU

Addr: 0xAC

Power Dist Board

AT24C02 (FRU)

Addr: 0xAA

MCH_SPD0_SMB*

MCH_SPD1_SMB*

MCH_SPD2_SMB*

MCH_SPD3_SMB*

5VSTBY

SMB_SMLINK_3V3SB_*

PCIe HP

Controller

(TPS2363)

Addr: 0x8C

Slot # 1 & 2

0-ohm

(empty)

SMB_CPU_3V3_*

SAS_Riser

SDTA/SCLK

(0xC4)

0-ohm

0-ohm

(empty)

3V3STBY

3V3STBY

3V3STBY

0-ohm

0-ohm

SMB_SYS_PWR_*

NE1617

Temp Sensor

(Addr: 0x30)

NE1617

Temp Sensor

(Addr: 0x98)

NE1617

Temp Sensor

(Addr: 0x9C)

3V3

DB1200G

(0xDE)

FSB

3V3

DB1900G

(0xD8)

FBD, Branch0

PCIe Hot-Plug

I/O Port

(PCA9555)

Addr: 0x40

MSMBDAT/MSMBCLK

89HPES24N3A

(PCIe Expander)

Slot # 1 & 2

SSMBDAT/SSMBCLK

(Addr: 0xE0)

89HPES24N3A Slave SMBus

supports ARP (SMBus

address resolution protocol)

PCIE_HP12_SMB*

3V3

CK410B

(0xD2)

Note: PCIe SMBus is

NOT supported. 0-ohm

option is just a provision

and not a supported

feature.

3V3STBY

3.3V

3.3V

SMB_MEM_3V3_*

0-ohm

(empty)

SMB_SAS_3V3SB_*

SMB_CPU_3V3_*

Note: LM75 is a

placeholder

PSMI

Addr: 0xB0

PSMI

Addr: 0xB2

Advanced

I2C POST

Card

(Addr: 0xE0,

0x70, 0x76)

SMBus

Isolation

3V3STBY

3V3

Temp

Addr: 0x90

FRU

Addr: 0xAC

SMBus

Isolation

3V3

VSC410

SDA1/SCL1

SDA2/SCL2

SDA3/SCL3

Repeater

PCA9515

3V3STBY

3V3STBY

ESB2

3.3V

5V

3.3V

0-ohm

IO Expander

PCA9554

Addr: 0x42

,

,

0-ohm

0-ohm

Bootstrap

EEPROM

Addr: 0xA8

SAS

Controller

I2C0

I2C1

FRU

Addr: 0xA6

VSC410

0-ohm

(empty)

0-ohm

(Empty)

Repeater

PCA9515

0-ohm

Note: CPU SMBus is NOT supported. 0-ohm

option is just a provision and not a supported

feature. CPU1 SMBus address conflicts with SAS

Riser FRU SMBus address if the CPU SMBus is

connected for debugging.

Empty

Note: NE1617 Temp Sensor on the memory board is a

placeholder (backup plan). Fox Cove POR is FBD Closed

Loop Throttling using AMB Temp Sensor. However,

Temp Sensors will still be stuffed on Mem Riser as a “real-

time” in system backup plan.

SMB_SENSOR_SEG2_3V3SB_*

SMB_CS_MEM_SEG5_*

SMB_IPMB_*

0-ohm

empty

FRU

Addr: 0xA8

0-ohm

empty

Note: SMB_SMLINK_3V3SB_* is not

connected to any devices in the

default configuration. If connected to

a SMBus, it will be connected to only

one SMBus and so both the 0-ohms

will not be stuffe d at the same time.

If it is connecte d to ICH6 SMBCLK/

DATA, SMLINK0/1 will have to

change it’s slave address to 0x88.

CNB PCIE

HP SMbus

Not used

Fan fail LEDs

Fan presence,

System Type

(empty)

0-ohm

SMB_CS_SAS_*

Debug Only

PWR: 3V3

SMBus

Translation

3V3STBY

SMB_SAS_3V3SB_*

Note: SAS Backplane FRU SMBus

address needs to be changed if the

SMBus isolation is populated.

SAS RAID

DIMM

Addr: 0xA2

PCA9543

SMB Switch

IBBU

Header

Addr:

0x14, 0x16

SMBus

Isolation

(Empty)

SES

Header

SES

Header

AT24C64

FRU

(Addr: 0xA0)

0-ohm

empty

0-ohm

empty

0-ohm

empty

VID_DDC_*_REAR VID_DDC_*_FRONT

CRT2DDCDAT/

CRT2DDCCLK

SMBus

Translation

SMBus

Translation

5V

3.3V

3.3V

HPDTA/HPCLK

(PCIE HP)

3.3V

3V3STBY

3V3STBY

SMLINK0/1 (Slave)

Addr 0x44

SMLink0=CLK

SMLink1=Data

OEM

Header

(0x9E)

(0xA6)

SMBD3/SMBCLK3

SMBD4/SMBCLK4

SMBD2/SMBCLK2

FLBSD1/FLBSINTEX1

SMBD1/SMBCLK1

FLBSD0/FLBSINTEX0

SMBD0/SMBCLK0

(TCO)

3V3STBY

3V3STBY

3V3STBY

3V3STBY

SMBus

Isolation

USB

EEPOM

(0xA0)

Empty

Note: FP Board USB HUB & EEPROM

SMBus addresses ne ed to be changed if

the SMBus isolation is populated.

EMPTY

3.3V

SMBus

Isolation

0-ohm

0-ohm

Figure 9. SMBus Block Diagram

Loading...

Loading...