BIOS Error Handling ESB2 BMC Core TPS

Revision 1.0

Intel order number E18291-001

234

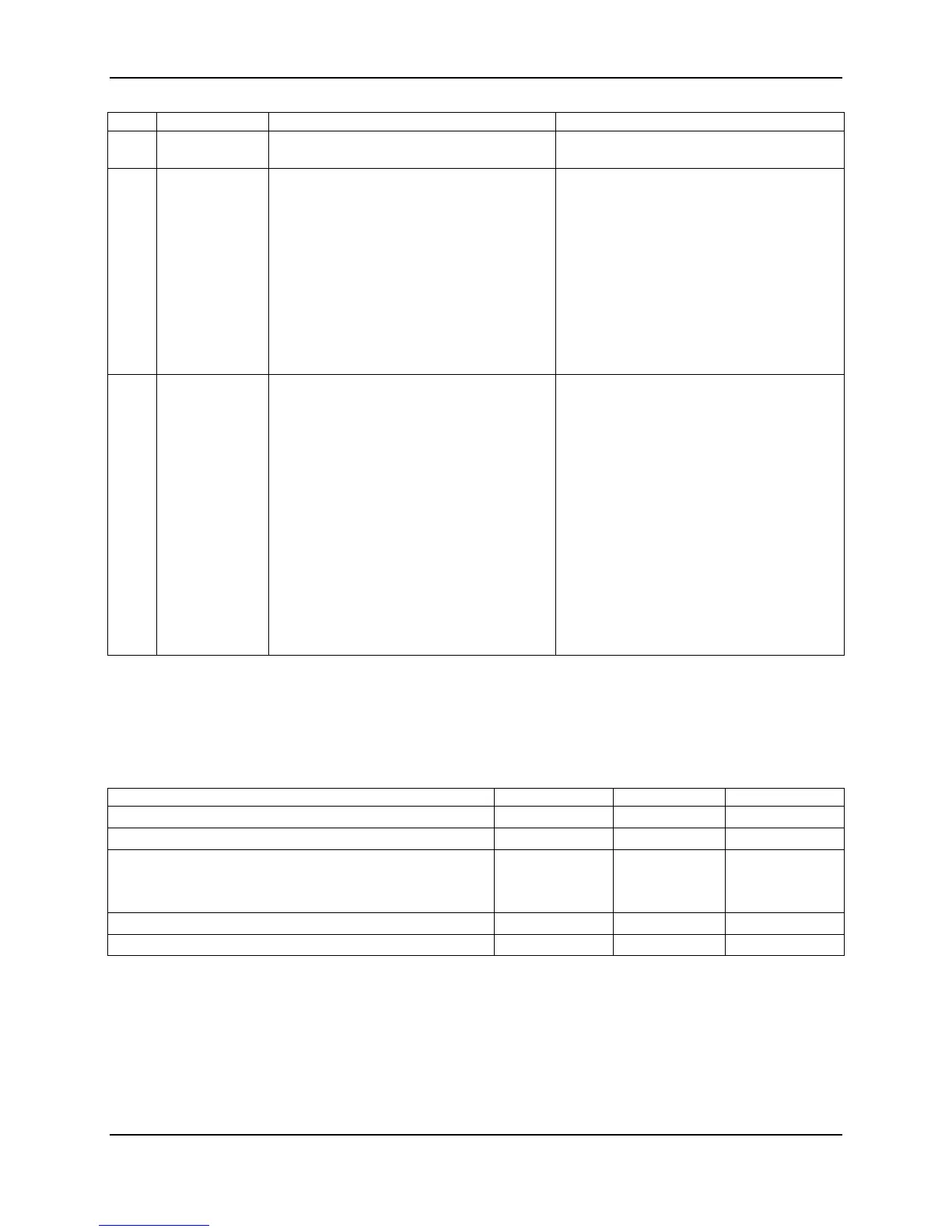

Byte Field IPMI Description BIOS Implementation

Interface Specification, Version 2.0, Table

42-3 for the event.

15 Event Data 2

(ED2)

Bit [7:0]

OEM value or unspecified

The BIOS sends this to the BMC:

For PCI PERR and SERR events:

PCI bus number on which the

reporting device resides

If the error handler is unable to

determine the PCI address of the

device reporting the error, then ED1

reports ED2 as unspecified and ED2

contains 0xFF.

For Fatal NMI events:

0xFF = ED2 unspecified

16 Event Data 3

(ED3)

Bit [7:0]

OEM value or unspecified

The BIOS sends this to the BMC:

For PCI PERR and SERR events:

PCI device and function address of the

reporting device in the following format:

If the error handler is unable to determine

the PCI address of the device reporting the

error, then ED1 reports ED3 as unspecified

and ED3 contains 0xFF.

Bit[7:3] - Device number of the

reporting PCI device

Bit[2:0] - Function number. (Will

always contain a zero if the device is

not a multifunction device.)

For Fatal NMI events:

0xFF = ED2 unspecified

The following examples are provided to clarify SEL entry Event Data values for various events.

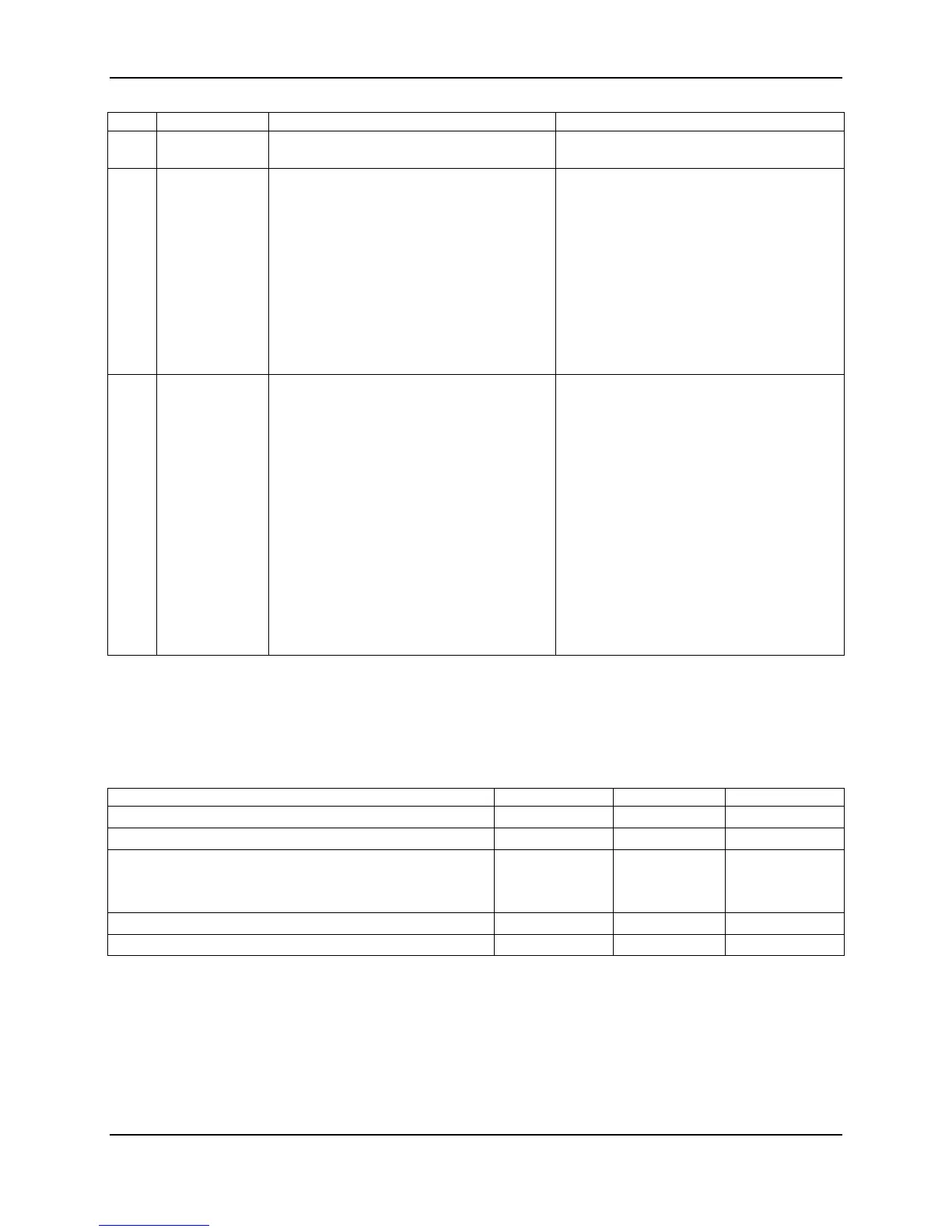

Table 91. SEL Entry Format — Critical Interrupt Sensor Type Examples

Error Type Event Data 1 Event Data 2 Event Data 3

PCI PERR, failing device is not known 0x04 0xFF 0xFF

PCI SERR, failing device is not known 0x05 0xFF 0xFF

PCI PERR on PCI Bus 5, Device 3, Function 1 0xA4 0x05 0x19

Bit[7:3] = 03

Bit[2:0] = 01

PCI SERR on PCI Bus 0 with device and function unknown 0x85 0x00 0xFF

Software NMI generated by SMI handler on fatal error 0x09 0xFF 0xFF

Loading...

Loading...