Intel® Server System S7000FC4UR TPS Main Board

Revision 1.0

27

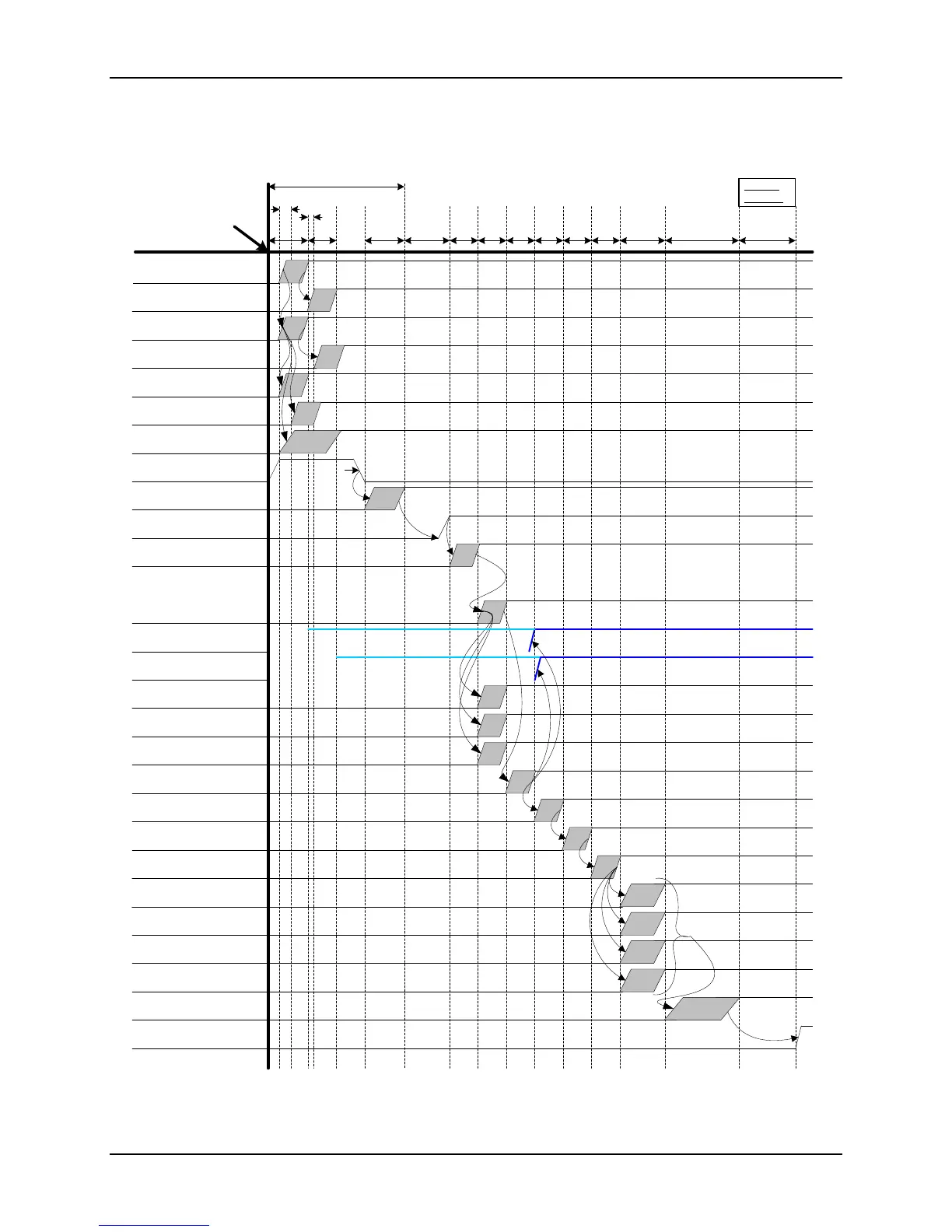

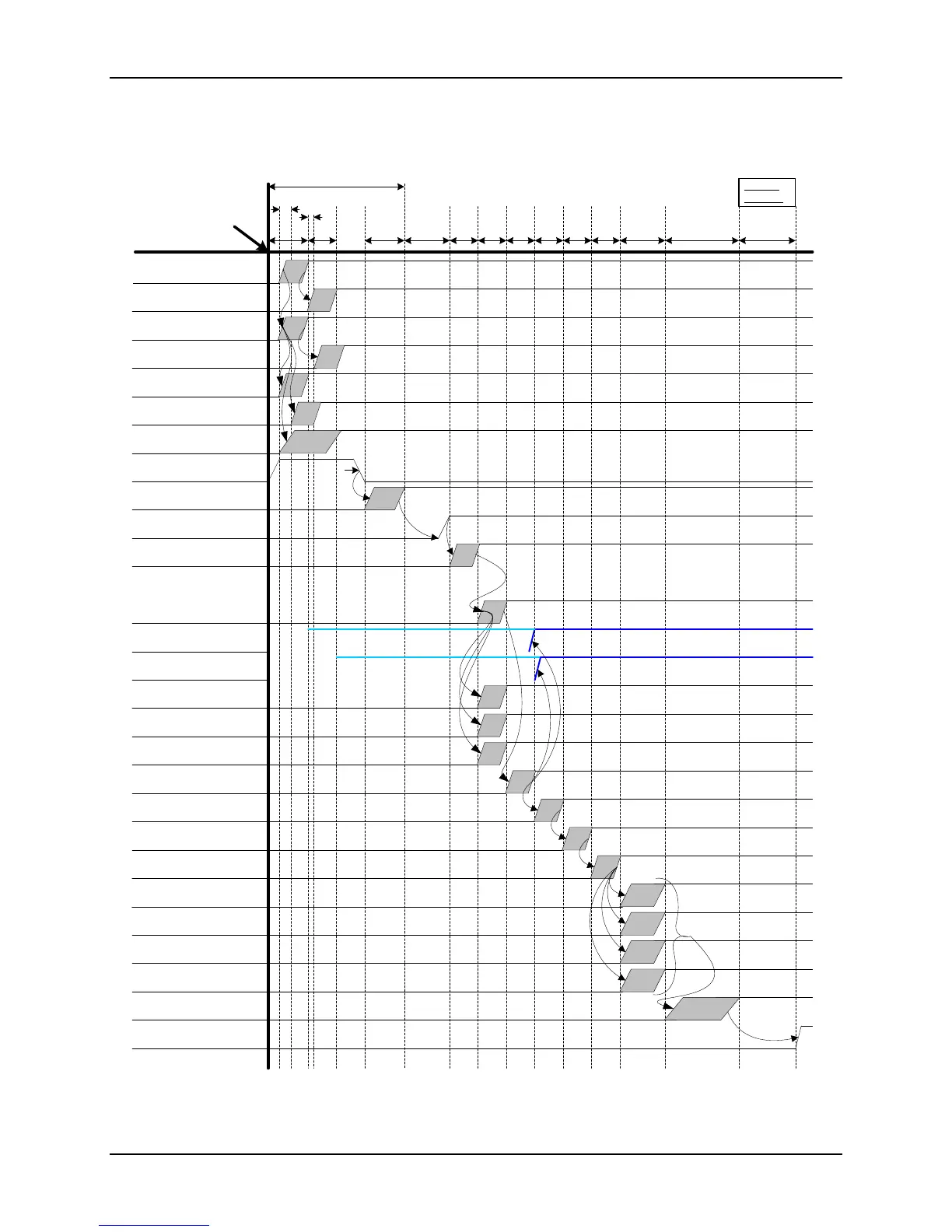

2.2.23 Power Sequencing/Timing Diagrams

2.2.23.1 Power-Up Sequencing Diagram

P12V

P5V

P3V3_STBY

PS_ON_N

P3V3

P1V8

P_VTT

(1.1V/1.2V selectable)

PS_PWROK

P1V5

AC Plug-In

2.0s

max

Wait for PS_ON_N

When all are good

Time not to scale

P3V3_AUX

P1V5_AUX

P1V9_NIC

P_VCCP1

P_VCCP2

10ms

max

P3V3_AUX

(switches from aux to main 3.3V power)

P1V5_ESB

P1V2_NIC

Rev 2.0

12/19/06

P5V_STBY

P1V8_DDR2

P1V2

P1V0

P_VCCP3

P_VCCP4

SYS_PWRGD

System Boards Power

Up Sequencing

P1V5_AUX

(driven by P3V3_AUX from 3.3V power)

5ms

to

400ms

100ms

to

500ms

3.0s max

10ms

max

10ms

max

10ms

max

10ms

max

10ms

max

20ms

max

180ms

max

100ms

min

20ms

max

IO_RISER_PWRGD

PLD Delay

Note: The BMC allows ~ 8 seconds for the

SYS_PWRGD signal to assert/deassert

before checking for power fault conditions

2ms

min

10ms

max

Figure 6. Main Board Power Sequencing Diagram

Loading...

Loading...