Intel® Server System S7000FC4UR TPS BIOS Error Handling

Revision 1.0

233

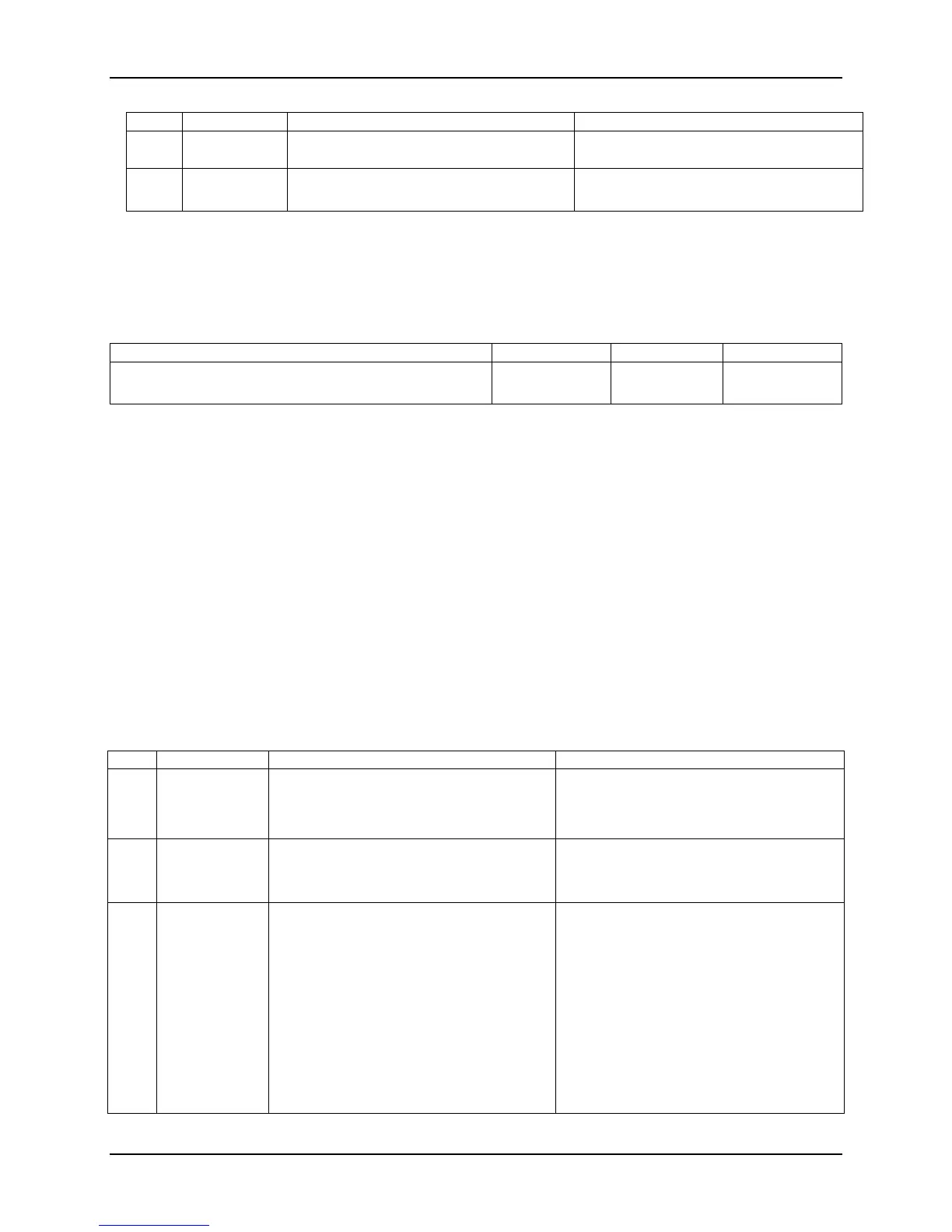

Byte Field IPMI Description BIOS Implementation

Bit [5:0] - Index into SMBIOS Type17

record for the failed FBDIMM

16 Event Data 3

(ED3)

Bit [7:0]

OEM value or unspecified

BIOS sends following information to BMC:

0xFF = ED3 unspecified

The following examples are provided to clarify SEL entry Event Data values for various events.

Table 89. SEL Entry Format — Event Logging Disabled Sensor Type Examples

Error Type Event Data 1 Event Data 2 Event Data 3

Correctable Memory Error Logging Disabled

Memory Riser Board A, FBDIMM 6

0x80 0x06 0xFF

19.2.7 IPMI Sensor Type Events — Critical Interrupt

The BIOS is responsible for logging SEL entries for the following events according to the format

described in the table below:

Sensor Offset 04h — PCI PERR Event

Sensor Offset 05h — PCI SERR Event

Sensor Offset 0Ah — Fatal NMI (port 61h, bit 7) Event

See the Intelligent Platform Management Interface Specification, Version 2.0, Intel Corporation

Table 42-3 for the following implementation details:

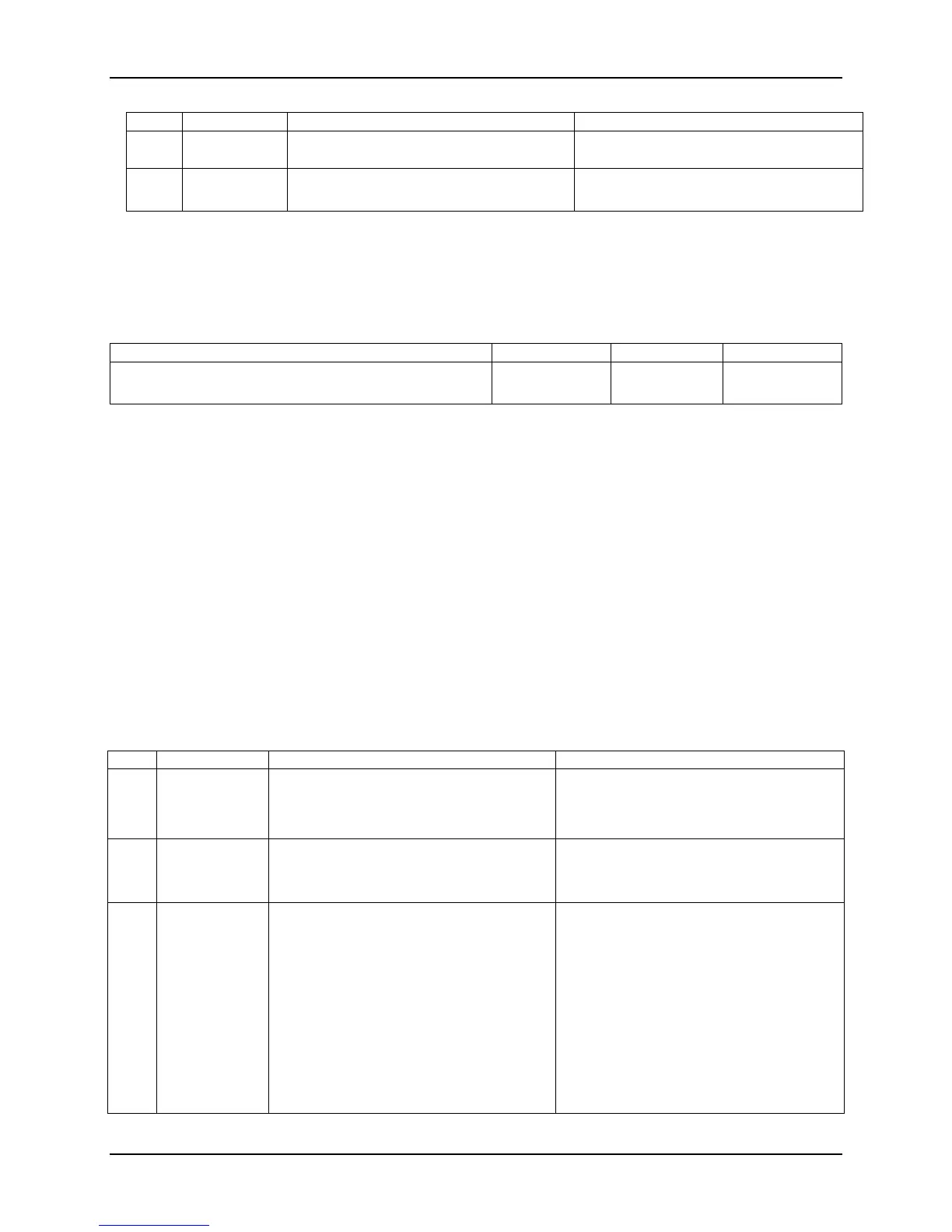

Table 90. SEL Entry Format — Critical Interrupt Sensor Type

Byte Field IPMI Description BIOS Implementation

11 Sensor Type See the Intelligent Platform Management

Interface Specification, Version 2.0, Intel

Corporation Table 42-3 Sensor Type Code

for allowable values.

The BIOS sends this to the BMC:

0x13 = Critical Interrupt

12 Sensor

Number

Number of sensor that generated this

event.

The BIOS sends this to the BMC:

0xEA = PCI PERR

0xEB = PCI SERR

14 Event Data 1

(ED1)

Bit [7:6]

00b = ED2 unspecified

10b = ED2 contains OEM value

Bit [5:4]

00b = ED3 unspecified

10b = ED3 contains OEM value (The

BIOS not use encodings 01b or 11b

for errors discussed in this

document.).

Bit [3:0]

See the Intelligent Platform Management

The BIOS sends this to the BMC:

Bit[7:6] = ED2 encoding varies by event

Bit[5:4] = ED3 encoding varies by event

Bit[3:0] - Supported Sensor Offsets

0x4 — PCI PERR

0x5 — PCI SERR

0x9 — Fatal NMI (port 61, bit7)

Loading...

Loading...