Intel® Server System S7000FC4UR TPS Main Board

Revision 1.0

13

PLD1

TPM

CK410B

DB1900G_BRANCH0_P/N

ESB2E

ESB_USB_48MHZ_CLK

14MHz

Crystal

DB1900G

Branch0

(PLL Mode)

(High BW)

ESB_SATA_CLK_P/N

ESB_PE_SRC_P/N

ESB_ESI_SRC_P/N

ESB_14MHZ_CLK

ESB_PCI_33MHZ_CLK

SUSCLK

MCH_BCLK_P/N

XDP1_BCLK_P/N

32.7KHz

Crystal

2

2

2

2

CPU_0P/N

CPU_1P/N

CPU_2P/N

CLK_INP/N

DIF_0P/N

DIF_1P/N

DIF_2P/N

DIF_3P/N

DIF_4P/N

DIF_5P/N

DIF_6P/N

DIF_17P/N

SRC_1P/N

SRC_4P/N

SRC_3P/N

SRC_2P/N

SRC_0P/N

SATACLKP/N

PECLKP/NESICLK100P/N

Gilgal LOM

25MHz

Crystal

SK_LAN_CLK

SMA

Connector

USB_48

REF_0

PCI_1

PCI_0

PCIF_2

PCI_3

PCIF_1

PCI_2

CLK48

CLK14

PCICLK

SUSCLK

SER_CLK_IN

PHY_CLK_OUT

PCIF_0

REF_1

EBUS_CLK_2

EBUS_CLK_2

2

DB1900G_SRC_P/N

RN50 Video

PCICLK

MEM_CLKP/N

IO_RISER_33MHZ_CLK

Rev 2.1

1/26/07

CPU1

BCLK0/1

CPU2

BCLK0/1

DB1200G

Host

(PLL Mode)

(High BW)

DIF_1P/N

DIF_7P/N

DIF_6P/N

DIF_3P/N

DIF_2P/N

DIF_0P/N

XDP1 (CPUs)

Clarksboro

MCH

FBD23CLKP/N

FBD01CLKP/N

CPU3

BCLK0/1

CPU4

BCLK0/1

PECLKP/N

CORECLKP/N

DIF_7P/N

DIF_8P/N

DIF_9P/N

DIF_10P/N

DIF_11P/N

DIF_12P/N

DIF_13P/N

DIF_14P/N

DIF_15P/N

DIF_16P/N

DIF_18P/N

DB1900G

Branch1

(PLL Mode)

(High BW)

DB1900G

PCIe

(Bypass Mode)

DIF_15P/N

BCLK0/1

DIF_5P/N

CPU_3P/N

DIF_4P/N

27MHz

Crystal

XDP2 (CS)

BCLK0/1

MCH_SRC _P/N

DIF_13P/N

CLK

DB1900G_BRANCH1_P/N

2

222222222

CPU2_BCLK_P/N

CPU1_BCLK_P/N

XDP2_BCLK_P/N

CPU3_BCLK_P/N

CPU4_BCLK_P/N

2

2

2

2

2

2

DB1200G_BCLK_P/N

2

2

2

2

2

2

TPM_33MHZ_CLK

DIF_1P/N

DIF_2P/N

DIF_3P/N

DIF_4P/N

DIF_5P/N

DIF_6P/N

DIF_7P/N

DIF_8P/N

DIF_9P/N

DIF_10P/N

DIF_11P/N

DIF_12P/N

DIF_13P/N

DIF_14P/N

DIF_15P/N

DIF_16P/N

CLK_INP/N

DIF_0P/N

DIF_17P/N

DIF_18P/N

2

2

2

2

2

2

2

2

2

FBD_BRANCH0_CLK_P/N

FBD_BRANCH1_CLK_P/N

2

2

2

2

2

2

2

2

FBD_DIMMA1_CLK_P/N

FBD_DIMMA2_CLK_P/N

FBD_DIMMA3_CLK_P/N

FBD_DIMMA4_CLK_P/N

FBD_DIMMA5_CLK_P/N

FBD_DIMMA6_CLK_P/N

FBD_DIMMA7_CLK_P/N

2

2

2

2

2

2

2

2

FBD_DIMMB1_CLK_P/N

FBD_DIMMB2_CLK_P/N

FBD_DIMMB3_CLK_P/N

FBD_DIMMB4_CLK_P/N

FBD_DIMMB5_CLK_P/N

FBD_DIMMB6_CLK_P/N

FBD_DIMMB7_CLK_P/N

2

2

2

2

2

2

2

2

FBD_DIMMC1_CLK_P/N

FBD_DIMMC2_CLK_P/N

FBD_DIMMC3_CLK_P/N

FBD_DIMMC4_CLK_P/N

FBD_DIMMC5_CLK_P/N

FBD_DIMMC6_CLK_P/N

FBD_DIMMC7_CLK_P/N

SAS_RISER_SRC_P/N

DIF_11P/N

DIF_10P/N

DIF_9P/N

DIF_8P/N

FBD_DIMMA8_CLK_P/N

FBD_DIMMB8_CLK_P/N

FBD_DIMMC8_CLK_P/N

FBD_DIMMD1_CLK_P/N

FBD_DIMMD2_CLK_P/N

FBD_DIMMD3_CLK_P/N

FBD_DIMMD4_CLK_P/N

FBD_DIMMD5_CLK_P/N

FBD_DIMMD6_CLK_P/N

FBD_DIMMD7_CLK_P/N

FBD_DIMMD8_CLK_P/N

1:1

1:1

DIF_12P/N

DIF_16P/N

SUSCLK

DIF_14P/N

LCDCNTL_(3)

IO_RISERA_SRC_P/N

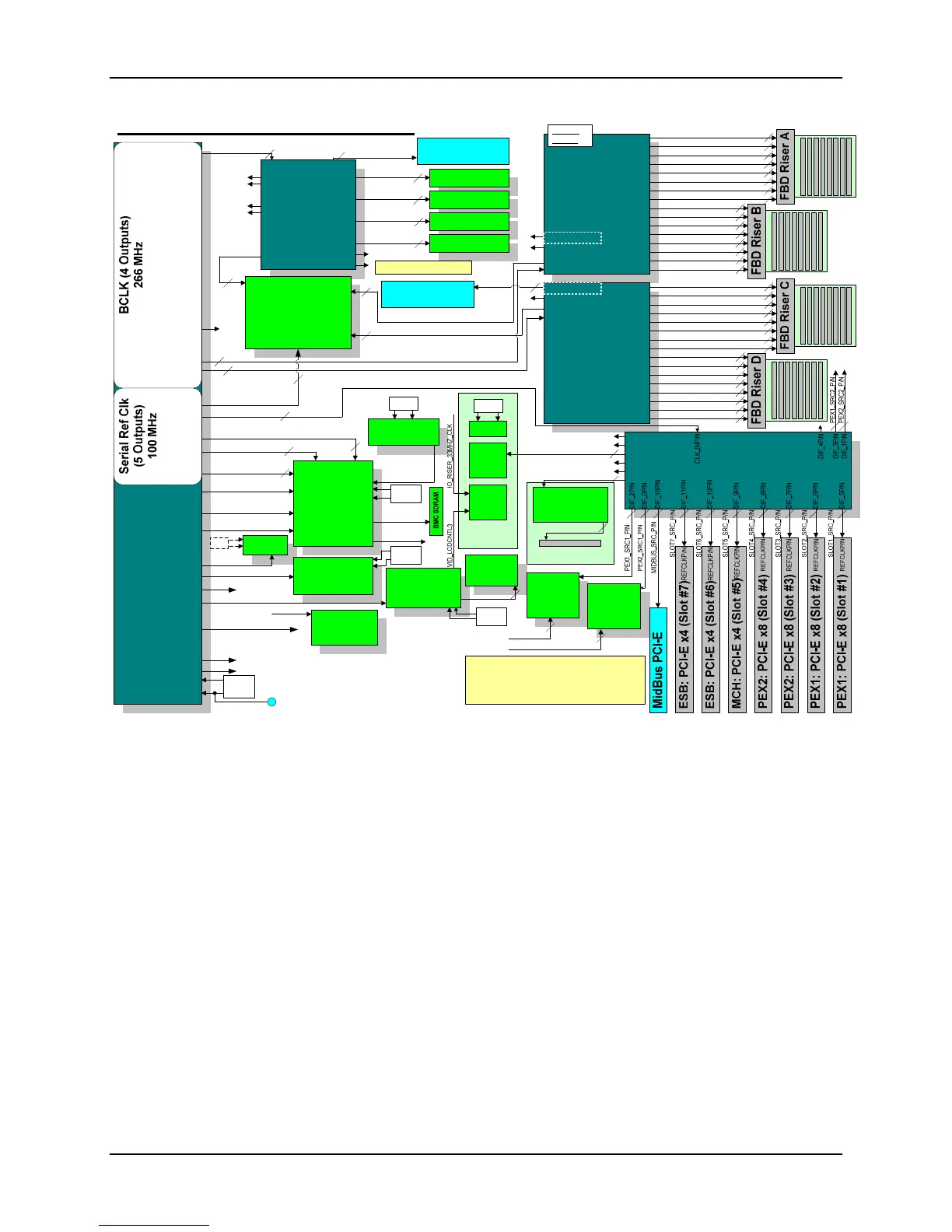

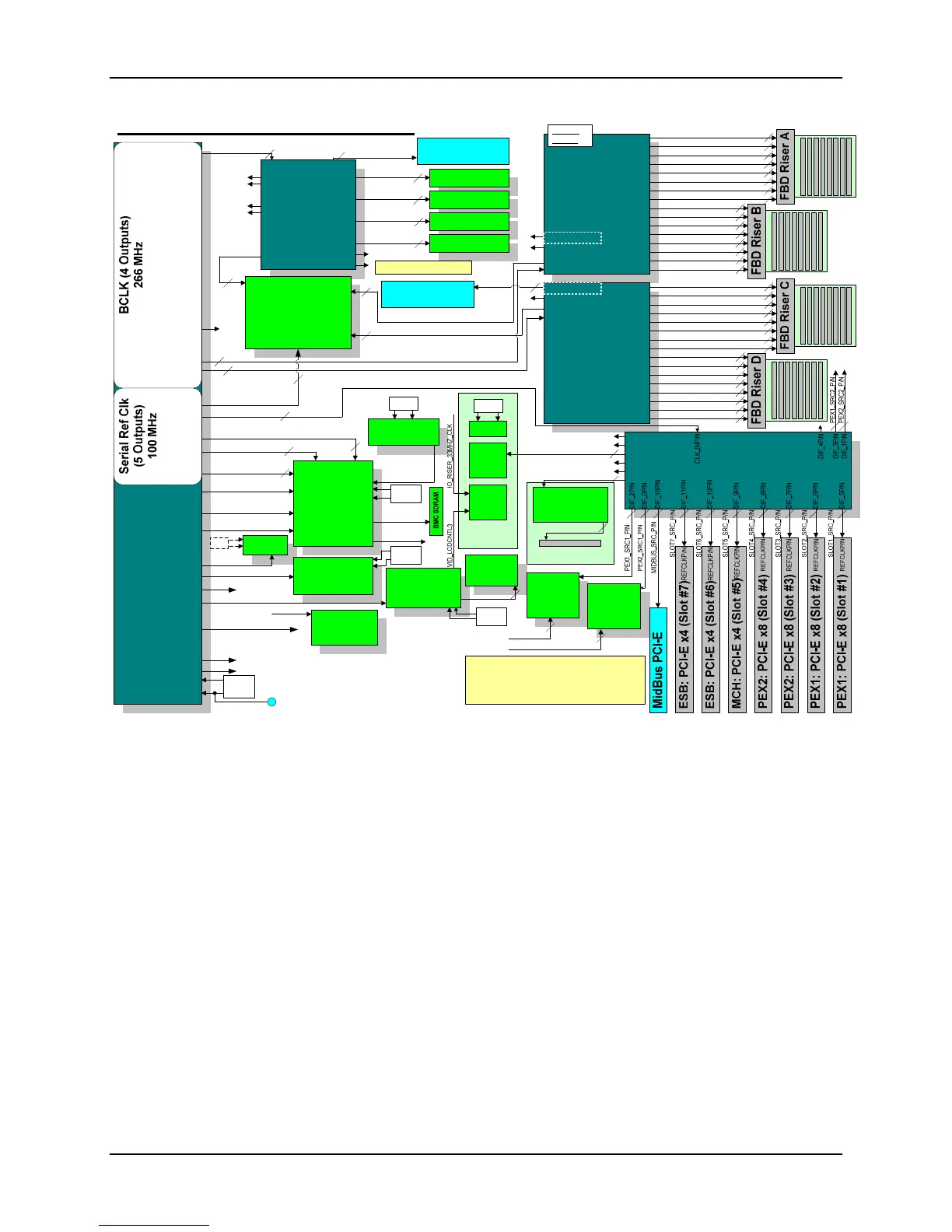

S7000FC4UR Server Clock Diagram

I/O Riser

RMM2

Zoar

LOM

GCM3

25MHz

Crystal

SIO3

LCLK

32.7KHz

Crystal

VIDEO_33MHZ_CLK

SAS Riser

SAS Ctrlr

(SAS)

DDR2 REG DIMM

2

REFCLKP/N

SAS_MEM_CLKP/N

*

*

*

*

*

SIO_33MHZ_CLK

Video

SDRAM

CLKP/N

PES1

X24

PES2

X24

CLK_INP/N

VID_MEM_CLKP/N

2

GCLK0

DIF_17P/N

2

32.7KHz

Crystal

Note 1: MidBus PCI-E block represents all MidBus probes

receiving the same SRC

Note 2: Some Clk pin assignments are subject to change based

on placement and routing

Note 3: SMBus Clks and JTAG Clks not shown in this diagram

REFCLK0P/N

REFCLK0P/N

REFCLK1P/N

REFCLK1P/N

PEX2_SRC2_P/N

PEX1_SRC2_P/N

22

2

2

= Clock in ganged topology

*

Figure 2. Main Board Clock Block Diagram

2.2.9.2 CK410B (Clock Generator/Synthesizer)

The CK410B clock generator/synthesizer is the main clock source for most of the devices on

the main board. Although it supports a maximum host clock frequency of 400 MHz, the main

board will only support at most 266 MHz for its supported processors.

Loading...

Loading...