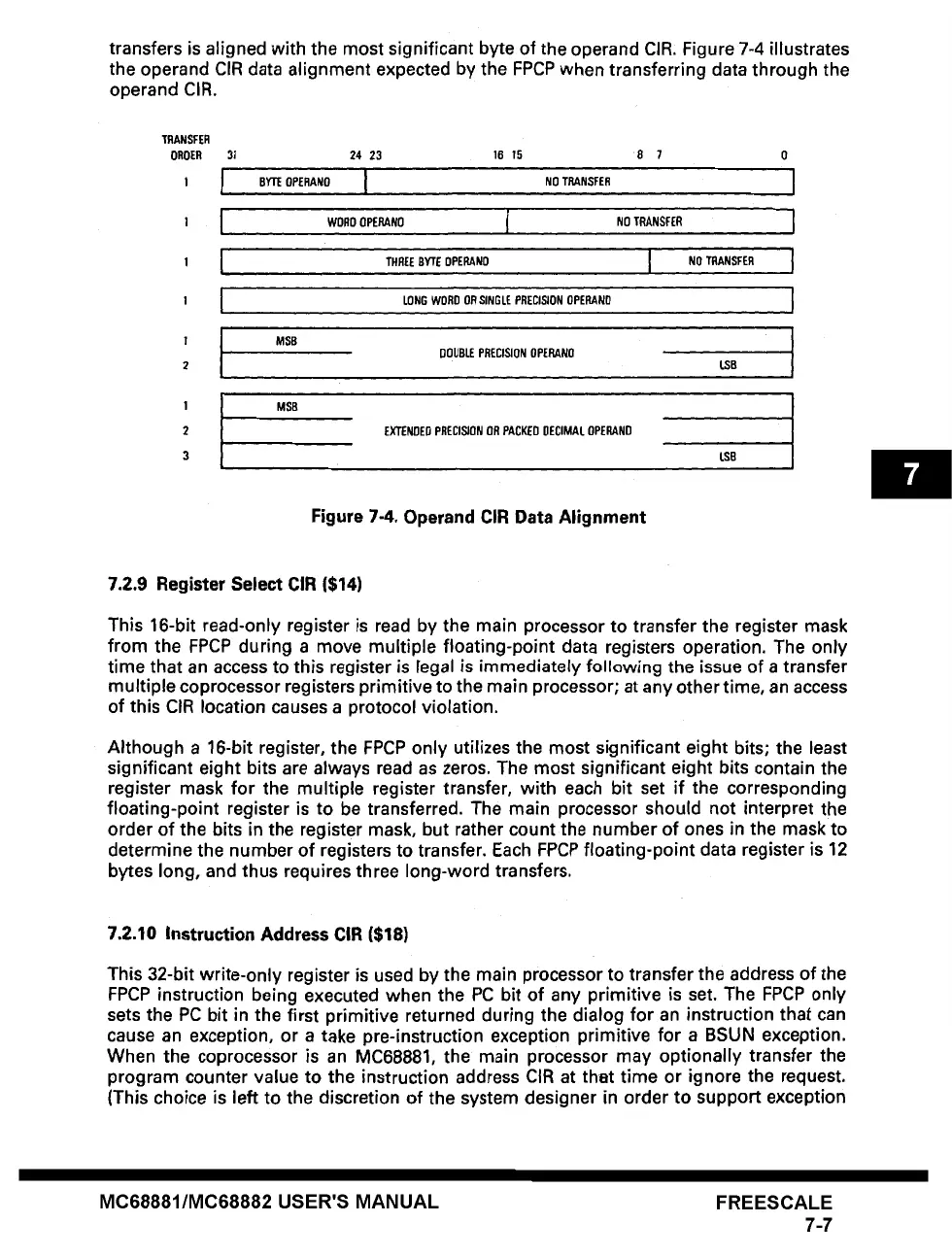

transfers is aligned with the most significant byte of the operand CIR, Figure 7-4 illustrates

the operand CIR data alignment expected by the FPCP when transferring data through the

operand CIR.

TRANSFER

ORDER

1

1

1

I

31 24 23 16 '15 8 7 0

J BYTE OPERANO ] NO TRANSFER J

I WORD OPERANO J, NO TRANSFER I

[ THREE BYTE OPERAND J NO TRANSFER J

LONG WORD DR SINGLE PRECISION OPERAND ]

MSB

DOU8LE PRECISION OPERANO

LSB

MSB

EXTENDED PRECISION OR PACKED DECIMAL OPEl]AND

LSR

Figure 7-4. Operand ClR Data Alignment

7.2.9 Register Select CIR ($14)

This 16-bit read-only register is read by the main processor to transfer the register mask

from the FPCP during a move multiple floating-point data registers operation. The only

time that an access to this register is regal is immediately following the issue of a transfer

multiple coprocessor registers primitive to the main processor; at any other time, an access

of this CIR location causes a protocol violation.

Although a 16-bit register, the FPCP only utilizes the most significant eight bits; the least

significant eight bits are always read as zeros. The most significant eight bits contain the

register mask for the multiple register transfer, with each bit set if the corresponding

floating-point register is to be transferred. The main processor should not interpret the

order of the bits in the register mask, but rather count the number of ones in the mask to

determine the number of registers to transfer. Each FPCP floating-point data register is 12

bytes long, and thus requires three long-word transfers.

7.2.10 Instruction Address CIR ($18)

This 32-bit write-only register is used by the main processor to transfer the address of the

FPCP instruction being executed when the PC bit of any primitive is set. The FPCP only

sets the PC bit in the first primitive returned during the dialog for an instruction that can

cause an exception, or a take pre-instruction exception primitive for a BSUN exception.

When the coprocessor is an MC68881, the main processor may optionally transfer the

program counter value to the instruction address CIR at that time or ignore the request.

(This choice is left to the discretion of the system designer in order to support exception

MC68881/MC68882 USER'S MANUAL FREESCALE

7-7

Loading...

Loading...