8

3. By returning the null (CA=l, IA=I) primitive during internal conversions for non-

concurrent instruction execution (e.g, FMOVE.<fmt>FPn,<ea> in the MC68881 or

FMOVE.W FPn,<ea> in the MC68882) before returning service request primitives to

complete the operation.

4. By returning the not-ready, come-again format code during internal operations re-

quired by the FSAVE instruction. The FPCP returns this format code in some cases

(as described in 6.4 CONTEXT SWITCHING) to enable it to store a smaller state frame,

and the MPU can process interrupts while waiting for the save operation to begin.

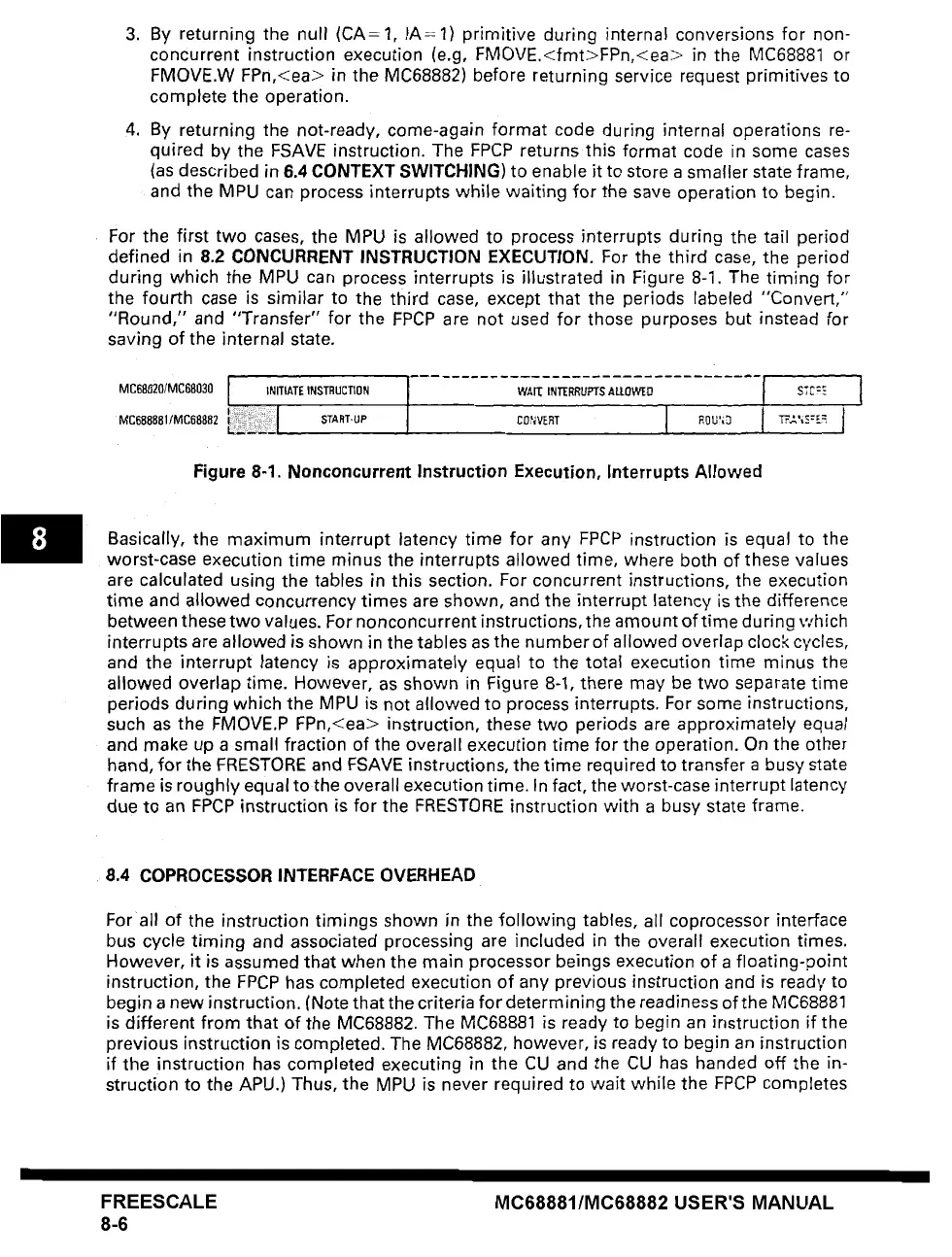

For the first two cases, the MPU is allowed to process interrupts during the tail period

defined in 8.2 CONCURRENT INSTRUCTION EXECUTION. For the third case, the period

during which the MPU can process interrupts is illustrated in Figure 8-1. The timing for

the fourth case is similar to the third case, except that the periods labeled

"Convert,"

"Round," and "Transfer" for the FPCP are not used for those purposes but instead for

saving of the internal state.

MC68020/MC68030

MC688881/MC68882

L! INITIATE INSTRUCTION

wAr~ ,Nr[RRU~rs AL~OW[O I STC=~

Figure 8-1. Nonconcurrent Instruction Execution, Interrupts Allowed

Basically, the maximum interrupt latency time for any FPCP instruction is equal to the

worst-case execution time minus the interrupts allowed time, where both of these values

are calculated using the tables in this section. For concurrent instructions, the execution

time and allowed concurrency times are shown, and the interrupt latency is the difference

between these two values. For nonconcurrent instructions, the amount of time during which

interrupts are allowed is shown in the tables as the number of allowed overlap clock cycles,

and the interrupt latency is approximately equal to the total execution time minus the

allowed overlap time. However, as shown in Figure 8-1, there may be two separate time

periods during which the MPU is not allowed to process interrupts. For some instructions,

such as the FMOVE.P FPn,<ea> instruction, these two periods are approximately equal

and make up a small fraction of the overall execution time for the

operation.

On the other

hand, for the FRESTORE and FSAVE instructions, the time required to transfer a busy state

frame is roughly equal to the overall execution time. In fact, the worst-case interrupt latency

due to an FPCP instruction is for the FRESTORE instruction with a busy state frame.

8.4 COPROCESSOR INTERFACE OVERHEAD

For all of the instruction timings shown in the following tables, all coprocessor interface

bus cycle timing and associated processing are included in the overall execution times.

However, it is assumed that when the main processor beings execution of a floating-point

instruction, the FPCP has completed execution of any previous instruction and is ready to

begin a new instruction. (Note that the criteria for determining the readiness of the MC68881

is different from that of the MC68882. The MC68881 is ready to begin an instruction if the

previous instruction is completed. The MC68882,

however,

is ready to begin an instruction

if the instruction has completed executing in the CU and the CU has handed off the in-

struction to the APU.) Thus, the MPU is never required to wait while the FPCP completes

FREESCALE

8-6

MC68881/MC68882 USER'S MANUAL

Loading...

Loading...