MAX32660 User Guide

Maxim Integrated Page 102 of 195

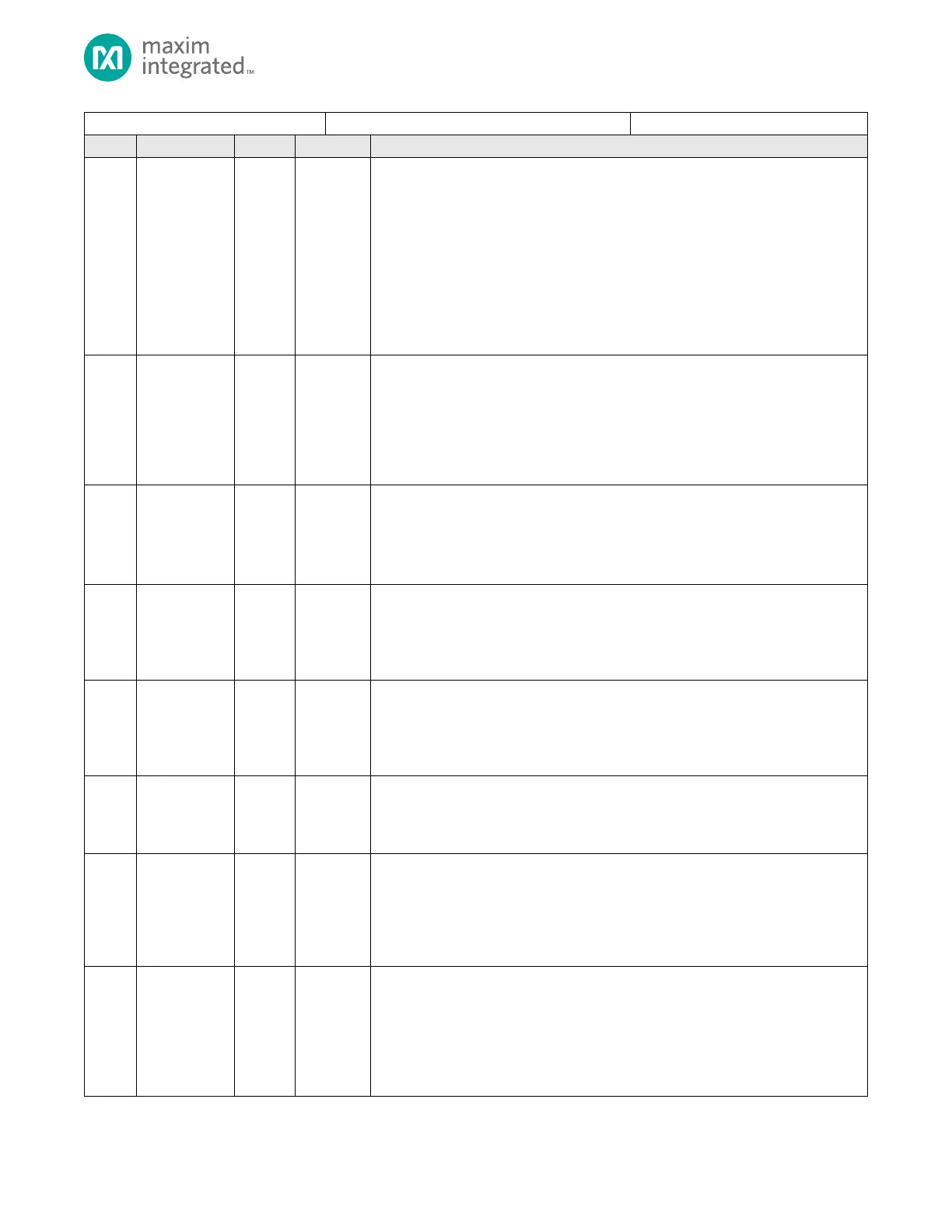

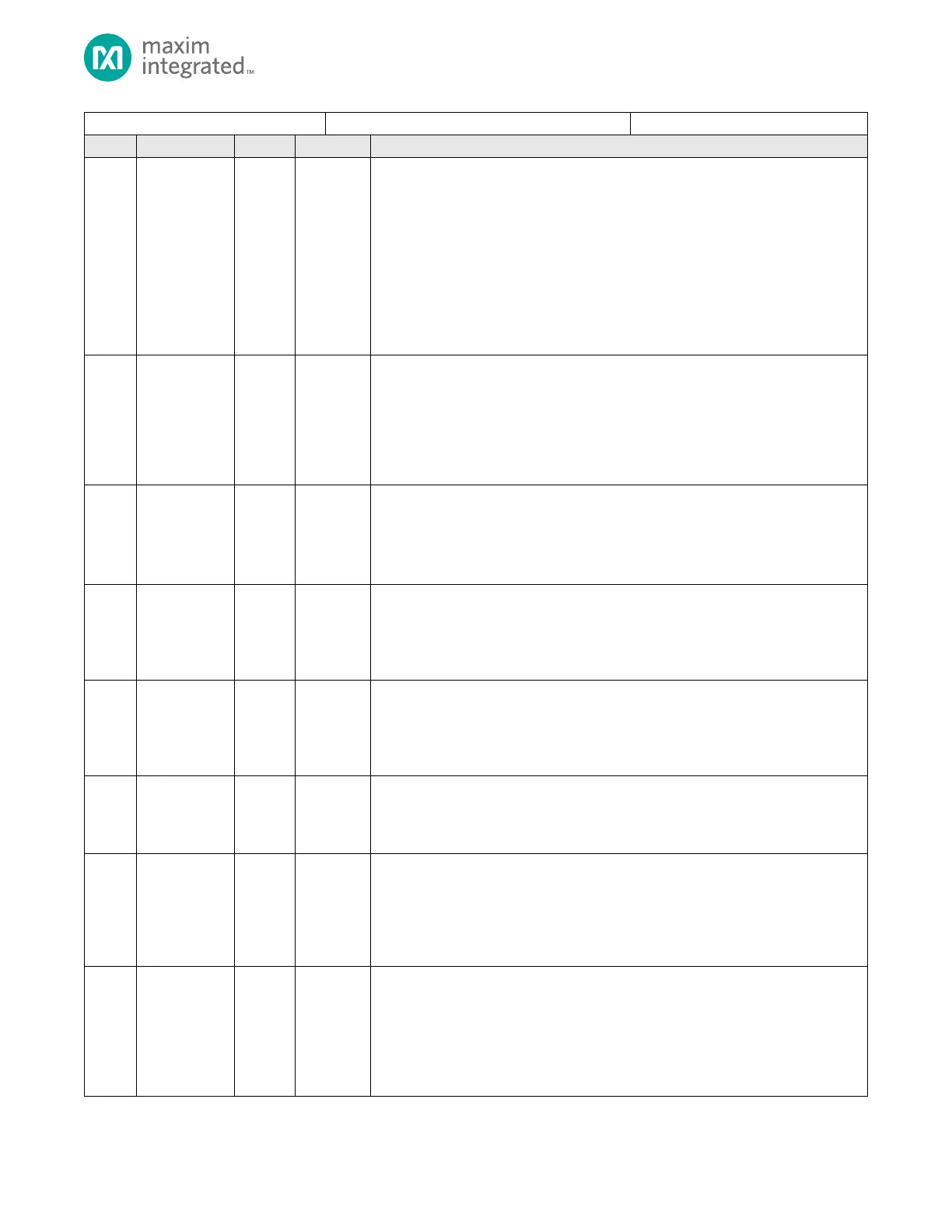

32kHz Oscillator Mode Select

Selects the operating mode for the 32kHz oscillator.

0: Operates in noise immunity mode

1: Operates in quiet mode. Oscillator warm-up is not required.

2: Operates in noise immunity mode when the processor is in active modes and

switches to quiet mode when the processor enters DEEPSLEEP. The system waits

for the 32kHz oscillator to warm-up prior to the processor exiting stop mode.

3: Operates in noise immunity mode when the processor is in active modes and

switches to quiet mode when the processor enters stop mode. The system does

not wait for the 32kHz oscillator to warm-up prior to the processor exiting stop

mode and beginning code execution.

Frequency Output Select

Selects the output frequency to output on the 32KCAL alternate function output pin if

the RTC_CTRL.32kout_en bit is set to 1 and the GPIO is enabled for the alternate pin

function 32KCAL; unused otherwise.

0b00: 1Hz (Compensated)

0b01: 512Hz (Compensated)

0b1x: 4kHz

Square Wave Output Enable

0: Square wave output disabled.

1: Square wave is output on the 32KCAL alternate function pin with the frequency

determined by the RTC_CTRL.freq_sel field.

Note: This bit is set to 0 on a POR and is not affected by other resets.

Sub-second Alarm Interrupt Flag

This interrupt flag is set when a sub-second alarm condition occurs. This flag is a

wake-up source for the processor.

0: No sub-second alarm pending.

1: Sub-second interrupt pending.

Time-of-Day Alarm Interrupt Flag

This interrupt flag is set by hardware when a time-of-day alarm occurs. This flag is a

wake-up source for the processor.

0: No Time-of-Day alarm interrupt pending.

1: Time-of-day interrupt pending.

RTC Ready Interrupt Enable

This interrupt flag is set when the RTC ready bit is set by hardware.

0: Interrupt disabled.

1: Interrupt enabled.

RTC Ready

This bit is set to 1 by hardware when the RTC_SEC register is updated. Software can

clear this bit at any time. Hardware automatically clears this bit just prior to updating

the RTC_SEC register, indicating the RTC is busy.

0: RTC_SEC register not updated.

1: RTC_SEC register updated.

RTC Busy Flag

This bit is set by hardware when changes to the RTC registers are synchronized. The

bit is automatically cleared by hardware when the synchronization is complete.

Software should poll this field for 0 after changing RTC registers to ensure the change

is complete prior to making any other RTC register changes.

0: RTC not busy.

1: RTC busy.

Loading...

Loading...