MAX32660 User Guide

Maxim Integrated Page 190 of 195

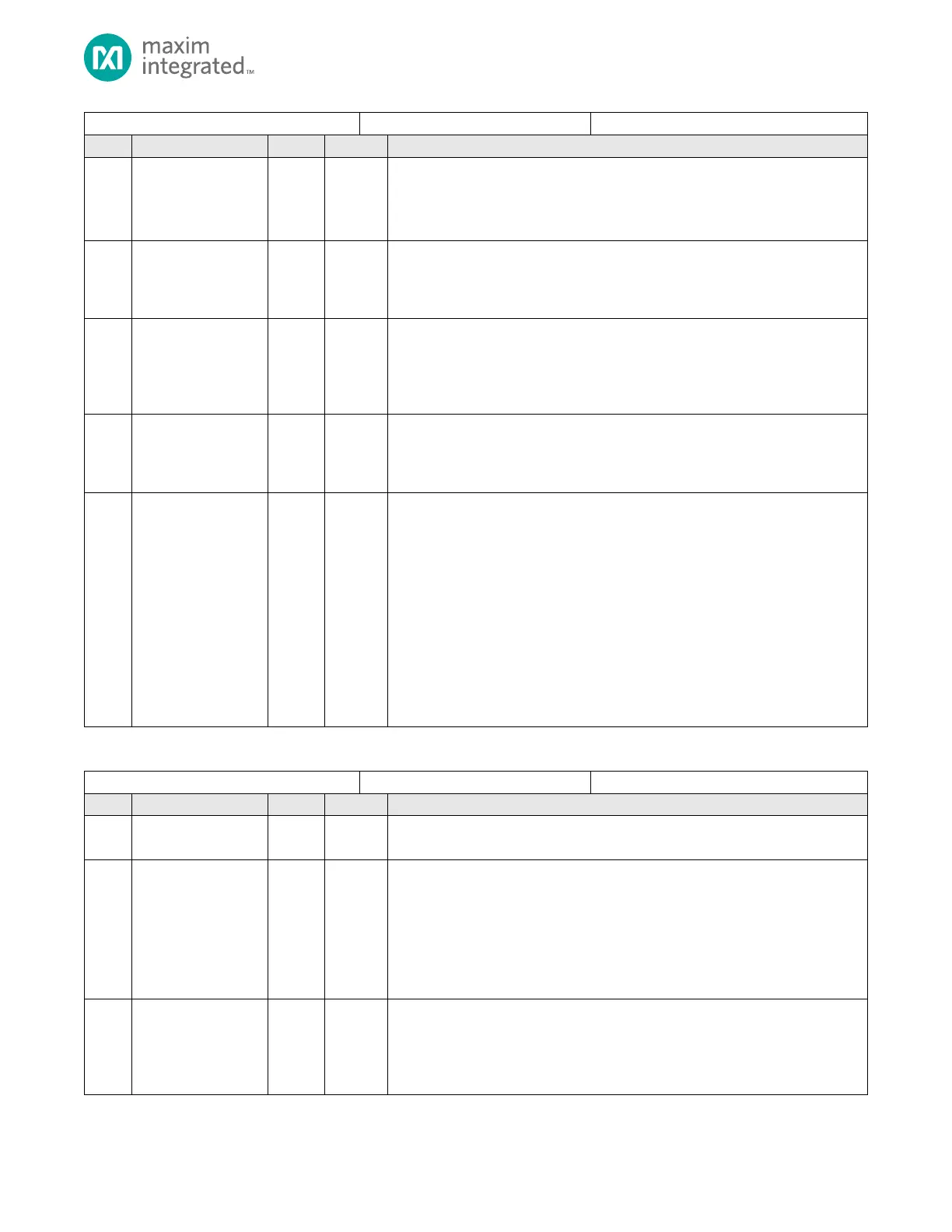

Phase Select

Refer to the section 13.3.7 Clock Phase and Polarity Control for details.

0: Data is valid prior to first serial clock edge.

1: Data transition occurs after the first serial clock edge.

Clock Polarity

Sets the idle state for the SCK clock pin after a character transaction.

0: SCK idles low (0) after character transmission or reception.

1: SCK idles high (1) after character transmission or reception.

Wired OR (Open Drain) Enable

Set to enable wired OR for the SPIMSS signal pins (SPI1_SCK, SPI1_SS0, SPI1_MOSI,

SPI1_MISO).

0: Wired OR configuration disabled.

1: Wired OR configuration enabled.

SPI Master Mode Enable

Set this field to enable master mode for SPI1.

0: SPI set to slave mode operation

1: SPI set to master mode operation

SPI1/I

2

S Enable

Set this field to enable operation of the SPIMSS as configured, either for SPI1 or

I

2

S. If the Transmit FIFO contains data, the data is considered valid and is

transmitted. If data is in the Receive FIFO, the data is considered valid and is used

as received data.

0: Disable SPI1 and I

2

S.

1: Enable SPI1 or I

2

S, if configured.

Note: This bit should be set to 1 only after the SPIMSS is configured for operation

as either SPI or I

2

S. Setting this bit to 0 does not reset or change any configuration

of the SPI or I

2

S and does not affect any data in the Transmit or Receive FIFOs.

Note: Clear the Transmit and Receive FIFOs, if desired, prior to setting this field to 1

by writing 1 to SPIMSS_DMA.tx_fifo_clr or SPIMSS_DMA.rx_fifo_clr respectively.

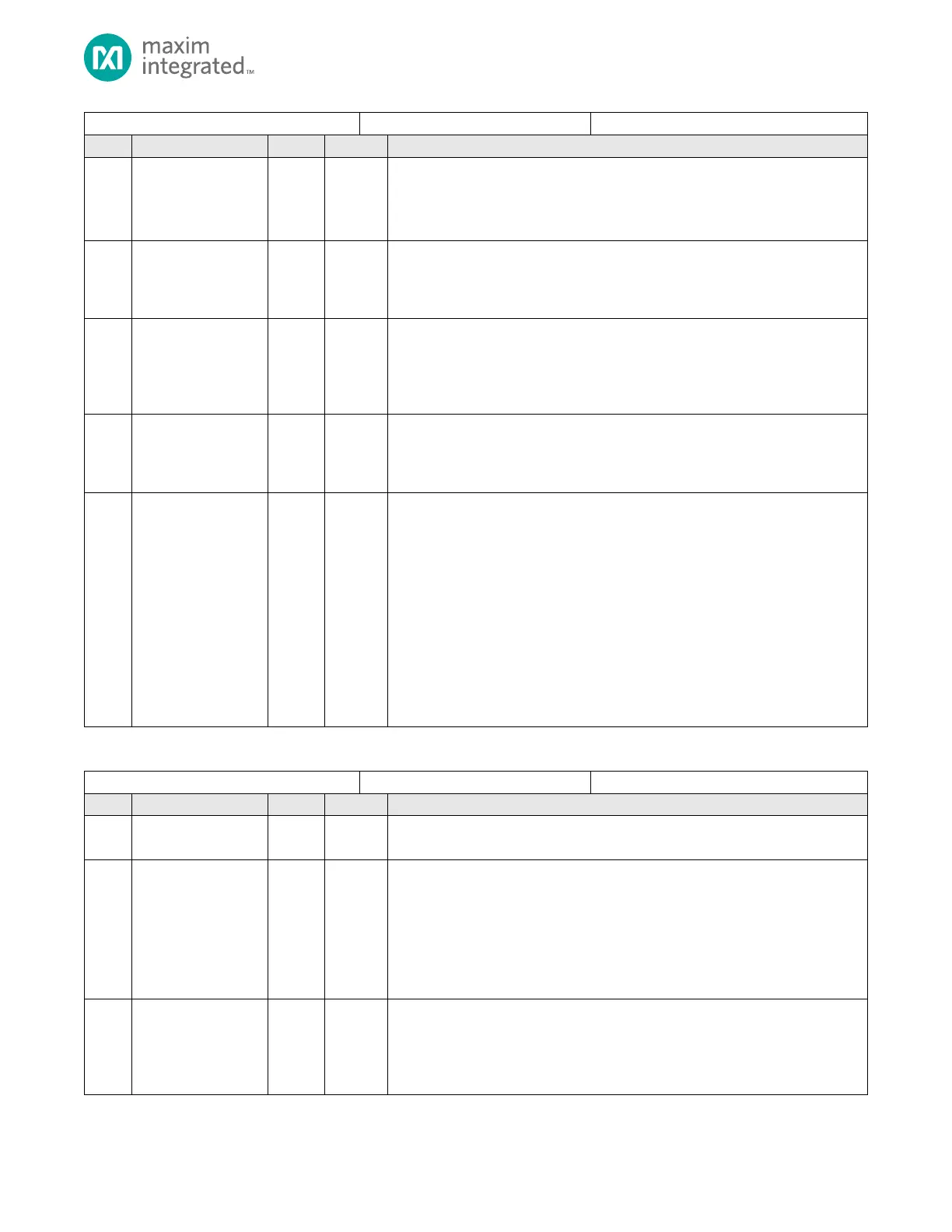

Table 14-8: SPIMSS Interrupt Flag Register

SPIMSS Interrupt Flag Register

Reserved for Future Use

Do not modify this field.

SPIMSS Interrupt Request Flag

This bit is set by hardware when an SPIMSS interrupt request is pending. Write 1

to clear.

0: No SPIMSS interrupt request is pending

1: An SPIMSS interrupt request is pending

Note: This field cannot be cleared unless all interrupt flags in this register are

cleared.

Transmit Overrun Flag

This bit is set by hardware when a transmit FIFO overrun has occurred. Write 1 to

clear.

0: No SPI interrupt request is pending

1: An SPI interrupt request is pending

Loading...

Loading...