MAX32660 User Guide

Maxim Integrated Page 127 of 195

11.2 Usage

Utilizing the watchdog timer in the application software is straightforward. As early as possible in the application software,

enable the watchdog timer interrupt and watchdog timer reset. Periodically the application software must write to the

WDT0_RST register to reset the watchdog counter. If program execution becomes lost, the watchdog timer interrupt will

interrupt routine may either attempt to repair the situation or allow the watchdog timer reset to occur. In the event of a

system software failure, the interrupt will not be executed, and the watchdog system reset will recover operation.

As soon as possible after a reset, the application software should interrogate the WDT0_CTRL.rst_flag to determine if the

reset event resulted from a watchdog timer reset. If so, application software should assume that there was a program

execution error and take whatever steps necessary to guard against a software corruption issue.

11.3 Interrupt and Reset Period Timeout Configuration

Each watchdog timer supports two independent timeout periods, the interrupt period timeout and reset period timeout.

Interrupt Period Timeout (WDT_CTRL0.int_period) - Sets the number of PCLK cycles until a watchdog timer interrupt is

generated. This period must be less than the Reset Period Timeout for the watchdog timer interrupt to occur.

Reset Period Timeout (WDT_CTRL0.rst_period) Sets the number of PCLK cycles until a system reset event occurs.

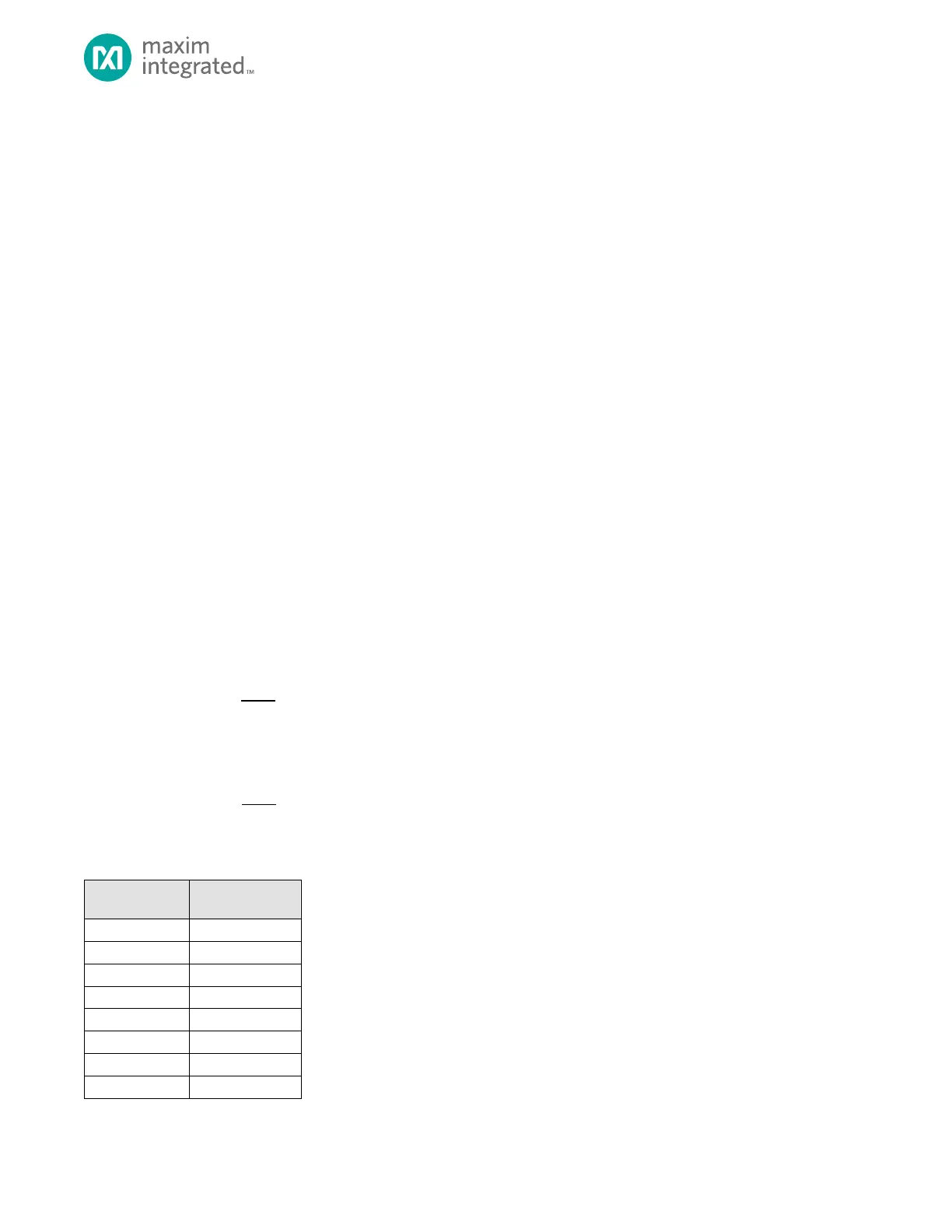

The interrupt and reset period timeouts are calculated using Equation 11-1 and Equation 11-2 respectively, where

. Table 11-1 shows example interrupt period timeout calculations for several WDT0_CTRL.int_period

settings with the System Clock set as the 96MHz High-Frequency Internal Oscillator.

Equation 11-1: Watchdog Timer Interrupt Period

Equation 11-2. Watchdog Timer Reset Period

Table 11-1: Watchdog Timer Interrupt Period with f

SYSCLK

= 96MHz and f

PCLK

= 48MHz

Loading...

Loading...